## Pin Descriptions

| PIN NUMBER | PIN NAME       | DESCRIPTION                                                                                             |                                                                                             |

|------------|----------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 1          | VDD            | Positive supply; connect this pin to a 2.25V to 3.3V supply.                                            |                                                                                             |

| 2          | GND            | Ground pin.                                                                                             |                                                                                             |

| 3          | REXT           | External resistor pin for ADC reference; connect this pin to ground through a (nominal) 500kΩ resistor. |                                                                                             |

| 4          | A <sub>0</sub> | Bit 0 of I <sup>2</sup> C address; ground or tie this pin to VDD. No floating.                          |                                                                                             |

| 5          | SCL            | I <sup>2</sup> C serial clock                                                                           | The I <sup>2</sup> C bus lines can be pulled from 1.7V to above V <sub>DD</sub> , 3.6V max. |

| 6          | SDA            | I <sup>2</sup> C serial data                                                                            |                                                                                             |

# **Principles of Operation**

#### Photodiodes and ADC

The ISL29020 contains two photodiode arrays which convert light into current. The spectral response for ambient light sensing and IR sensing is shown in Figure 8 in the "Typical Performance Curves" on page 9. After light is converted to current during the light signal process, the current output is converted to digital by a single built-in 16-bit Analog-to-Digital Converter (ADC). An I<sup>2</sup>C command reads the ambient light or IR intensity in counts.

The converter is a charge-balancing integrating type 16-bit ADC. The chosen method for conversion is best for converting small current signals in the presence of an AC periodic noise. A 100ms integration time, for instance, highly rejects 50Hz and 60Hz power line noise simultaneously. See "Integration Time or Conversion Time" on page 6 and "Noise Rejection" on page 7.

The built-in ADC offers user flexibility in integration time or conversion time. There are two timing modes: Internal Timing Mode and External Timing Mode. In Internal Timing Mode, integration time is determined by an internal oscillator ( $f_{OSC}$ ), and the n-bit ( $n=4,\,8,\,12,16$ ) counter inside the ADC. In External Timing Mode, integration time is determined by the time between two consecutive  $I^2C$  External Timing Mode commands. See "External Timing Mode" on page 6. A good balancing act of integration time and resolution depending on the application is required for optimal results.

The ADC has I<sup>2</sup>C programmable ranges to dynamically accommodate various lighting conditions. For very dim conditions, the ADC can be configured at its lower range (Range 1). For bright conditions, the ADC can be configured at its higher range (Range 2).

### P<sup>2</sup>C Interface

There are three 8-bit registers available inside the ISL29020. The command register defines the operation of the device. The command register does not change until the register is overwritten. The two data registers are Read-Only for 16-bit ADC output or timer output. The data registers contain the ADC's or timer's latest digital output.

The ISL29020's I<sup>2</sup>C interface slave address can be selected as 1000100 or 1000101 by connecting A0 pin to GND or VDD, respectively. When 1000100x or 1000101x with x as R or  $\overline{W}$  is sent after the Start condition, this device compares the first seven bits of this byte to its address and matches.

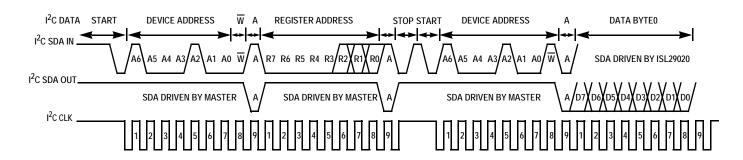

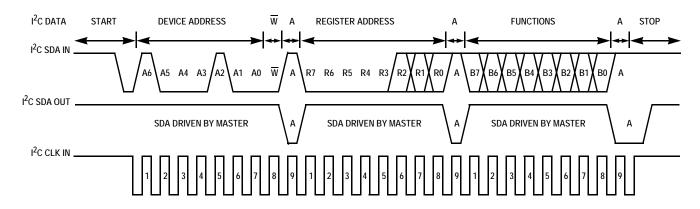

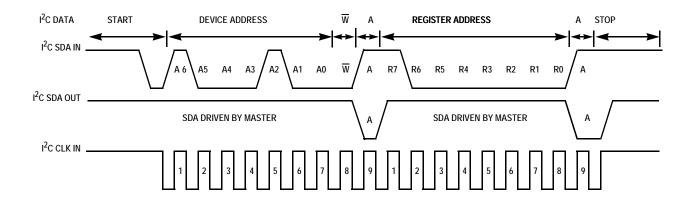

Figure 1 shows a sample one-byte read. Figure 2 shows a sample one-byte write. Figure 3 shows a sync\_I<sup>2</sup>C timing diagram sample for externally controlled integration time. The I<sup>2</sup>C bus master always drives the SCL (clock) line, while either the master or the slave can drive the SDA (data) line. Every I<sup>2</sup>C transaction begins with the master asserting a start condition (SDA falling while SCL remains high). The following byte is driven by the master, and includes the slave address and read/write bit. The receiving device is responsible for pulling SDA low during the acknowledgement period. Every I<sup>2</sup>C transaction ends with the master asserting a stop condition (SDA rising while SCL remains high).

For more information about the I<sup>2</sup>C standard, please consult the Philips<sup>®</sup> I<sup>2</sup>C specification documents.

#### Low-Power Operation

The ISL29020 initial operation is at the power-down mode after a supply voltage is provided. The data registers contain the default value of 0. When the ISL29020 receives an  $\rm I^2C$  command to do a one-time measurement from an  $\rm I^2C$  master, it will start light sensing and ADC conversion. It will go to the power-down mode automatically after one conversion is finished and keep the conversion data available for the master to fetch anytime afterwards. The ISL29020 will continuously do light sensing and ADC conversion if it receives an  $\rm I^2C$  command of continuous measurement. It will continuously update the data registers with the latest conversion data. It will go to the power-down mode after it receives the  $\rm I^2C$  command of power-down.

FIGURE 1. I<sup>2</sup>C READ TIMING DIAGRAM SAMPLE

FIGURE 2. I<sup>2</sup>C WRITE TIMING DIAGRAM SAMPLE

FIGURE 3. I<sup>2</sup>C SYNC\_I<sup>2</sup>C TIMING DIAGRAM SAMPLE