# MHT2080AH, MHT2060AH, MHT2040AH DISK DRIVES PRODUCT MANUAL

#### FOR SAFE OPERATION

#### **Handling of This Manual**

This manual contains important information for using this product. Read thoroughly before using the product. Use this product only after thoroughly reading and understanding especially the section "Important Alert Items" in this manual. Keep this manual handy, and keep it carefully.

FUJITSU makes every effort to prevent users and bystanders from being injured or from suffering damage to their property. Use the product according to this manual.

#### **IMPORTANT NOTE TO USERS**

READ THE ENTIRE MANUAL CAREFULLY BEFORE USING THIS PRODUCT. INCORRECT USE OF THE PRODUCT MAY RESULT IN INJURY OR DAMAGE TO USERS, BYSTANDERS OR PROPERTY.

While FUJITSU has sought to ensure the accuracy of all information in this manual, FUJITSU assumes no liability to any party for any damage caused by any error or omission contained in this manual, its updates or supplements, whether such errors or omissions result from negligence, accident, or any other cause. In addition, FUJITSU assumes no liability with respect to the application or use of any product or system in accordance with the descriptions or instructions contained herein; including any liability for incidental or consequential damages arising therefrom. FUJITSU DISCLAIMS ALL WARRANTIES REGARDING THE INFORMATION CONTAINED HEREIN, WHETHER EXPRESSED, IMPLIED, OR STATUTORY.

FUJITSU reserves the right to make changes to any products described herein without further notice and without obligation.

This product is designed and manufactured for use in standard applications such as office work, personal devices and household appliances. This product is not intended for special uses (atomic controls, aeronautic or space systems, mass transport vehicle operating controls, medical devices for life support, or weapons firing controls) where particularly high reliability requirements exist, where the pertinent levels of safety are not guaranteed, or where a failure or operational error could threaten a life or cause a physical injury (hereafter referred to as "mission-critical" use). Customers considering the use of these products for mission-critical applications must have safety-assurance measures in place beforehand. Moreover, they are requested to consult our sales representative before embarking on such specialized use.

The contents of this manual may be revised without prior notice.

The contents of this manual shall not be disclosed in any way or reproduced in any media without the express written permission of Fujitsu Limited.

All Rights Reserved, Copyright © FUJITSU LIMITED 2003

# **Revision History**

(1/1)

|         |            |                                                 | (1/                                        |

|---------|------------|-------------------------------------------------|--------------------------------------------|

| Edition | Date       | Revised section (*1)<br>(Added/Deleted/Altered) | Details                                    |

| 01      | 2003-06-20 |                                                 |                                            |

| 02      | 2003-10-28 | Table 1.2 (Altered)                             | Change of the order No.                    |

|         |            | Table 1.5 (Altered)                             | Change of the acoustic noise specification |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

|         |            |                                                 |                                            |

<sup>\*1</sup> Section(s) with asterisk (\*) refer to the previous edition when those were deleted.

## **Preface**

This manual describes about MHT2080AH/MHT2060AH/MHT2040AH out of the disk drive, 2.5-inch hard disk drives. These drives have a built-in controller that is compatible with the ATA interface.

This manual describes the specifications and functions of the drives and explains in detail how to incorporate the drives into user systems. This manual assumes that the reader has a basic knowledge of hard disk drives and their implementations in computer systems.

This manual consists of seven chapters and sections explaining the special terminology and abbreviations used in this manual:

#### **Overview of Manual**

#### **CHAPTER 1** Device Overview

This chapter gives an overview of the disk drive and describes their features.

#### **CHAPTER 2** Device Configuration

This chapter describes the internal configurations of the disk drive and the configuration of the systems in which they operate.

#### **CHAPTER 3** Installation Conditions

This chapter describes the external dimensions, installation conditions, and switch settings of the disk drive.

#### CHAPTER 4 Theory of Device Operation

This chapter describes the operation theory of the disk drive.

#### **CHAPTER 5** Interface

This chapter describes the interface specifications of the disk drive.

#### CHAPTER 6 Operations

This chapter describes the operations of the disk drive.

#### Glossary

The glossary describes the technical terms that need to be understood to read this manual.

#### **Acronyms and Abbreviations**

This section gives the meanings of the definitions used in this manual.

## **Conventions for Alert Messages**

This manual uses the following conventions to show the alert messages. An alert message consists of an alert signal and alert statements. The alert signal consists of an alert symbol and a signal word or just a signal word.

The following are the alert signals and their meanings:

This indicates a hazardous situation *could* result in *minor* or *moderate personal injury* if the user does not perform the procedure correctly. This alert signal also indicates that damages to the product or other property *may* occur if the user does not perform the procedure correctly.

#### **IMPORTANT**

This indicates information that could help the user use the product more efficiently.

In the text, the alert signal is centered, followed below by the indented message. A wider line space precedes and follows the alert message to show where the alert message begins and ends. The following is an example:

(Example)

**Data corruption:** Avoid mounting the disk drive near strong magnetic sources such as loud speakers. Ensure that the disk drive is not affected by external magnetic fields.

The main alert messages in the text are also listed in the "Important Alert Items."

# **Operating Environment**

This product is designed to be used in offices or computer rooms.

#### Conventions

An disk drive device is sometimes simply referred to as a "hard disk drive," "HDD," "drive," or "device" in this document.

Decimal numbers are represented normally.

Hexadecimal numbers are represented as shown in the following examples: X'17B9', 17B9h, 17B9H, or 17B9H.

Binary numbers are represented as shown in the following examples: 010 or 010b.

ii C141-E195-02EN

## **Attention**

Please forward any comments you may have regarding this manual.

To make this manual easier for users to understand, opinions from readers are needed. Please write your opinions or requests on the Comment at the back of this manual and forward it to the address described in the sheet.

# **Liability Exception**

"Disk drive defects" refers to defects that involve adjustment, repair, or replacement.

Fujitsu is not liable for any other disk drive defects, such as those caused by user misoperation or mishandling, inappropriate operating environments, defects in the power supply or cable, problems of the host system, or other causes outside the disk drive.

C141-E195-02EN iii

# **Important Alert Items**

# **Important Alert Messages**

The important alert messages in this manual are as follows:

A hazardous situation *could* result in *minor* or *moderate personal injury* if the user does not perform the procedure correctly. Also, damage to the product or other property, *may* occur if the user does not perform the procedure correctly.

| Task             | Alert message                                                                                                                                                                                                                                                                                                                    | Page |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Normal Operation | Data corruption: Avoid mounting the disk near strong magnetic sources such as loud speakers. Ensure that the disk drive is not affected by external magnetic fields.  Damage: Do not press the cover of the disk drive. Pressing it too hard, the cover and the spindle motor contact, which may cause damage to the disk drive. | 3-7  |

|                  | <b>Static:</b> When handling the device, disconnect the body ground (500 k $\Omega$ or greater). Do not touch the printed circuit board, but hold it by the edges.                                                                                                                                                               |      |

# **Manual Organization**

MHT2080AH, MHT2060AH, MHT2040AH

DISK DRIVES PRODUCT MANUAL (C141-E195)

<This manual>

- Device Overview

- Device Configuration

- Installation Conditions

- Theory of Device Operation

- Interface

- Operations

MHT2080AH, MHT2060AH, MHT2040AH

DISK DRIVES MAINTENANCE MANUAL (C141-F065)

- Maintenance and Diagnosis

- Removal and Replacement Procedure

C141-E195-02EN vii

# **Contents**

| CHAPTER 1 | Device Overview                  | 1-1  |

|-----------|----------------------------------|------|

|           | 1.1 Features                     | 1-2  |

|           | 1.1.1 Functions and performance  | 1-2  |

|           | 1.1.2 Adaptability               | 1-2  |

|           | 1.1.3 Interface                  | 1-3  |

|           | 1.2 Device Specifications        | 1-4  |

|           | 1.2.1 Specifications summary     | 1-4  |

|           | 1.2.2 Model and product number   | 1-5  |

|           | 1.3 Power Requirements           | 1-5  |

|           | 1.4 Environmental Specifications | 1-8  |

|           | 1.5 Acoustic Noise               | 1-9  |

|           | 1.6 Shock and Vibration          | 1-9  |

|           | 1.7 Reliability                  | 1-10 |

|           | 1.8 Error Rate                   | 1-11 |

|           | 1.9 Media Defects                | 1-11 |

|           | 1.10 Load/Unload Function        | 1-11 |

|           | 1.11 Advanced Power Management   | 1-12 |

| CHAPTER 2 | Device Configuration             | 2-1  |

|           | 2.1 Device Configuration         | 2-2  |

|           | 2.2 System Configuration         | 2-3  |

|           | 2.2.1 ATA interface              | 2-3  |

|           | 2.2.2 1 drive connection         | 2-3  |

|           | 2.2.3 2 drives connection        | 2-4  |

| CHAPTER 3 | Installation Conditions 3-1                      |      |  |

|-----------|--------------------------------------------------|------|--|

|           | 3.1 Dimensions                                   | 3-2  |  |

|           | 3.2 Mounting                                     | 3-3  |  |

|           | 3.3 Cable Connections                            | 3-9  |  |

|           | 3.3.1 Device connector                           | 3-9  |  |

|           | 3.3.2 Cable connector specifications             | 3-10 |  |

|           | 3.3.3 Device connection                          | 3-10 |  |

|           | 3.3.4 Power supply connector (CN1)               | 3-10 |  |

|           | 3.4 Jumper Settings                              | 3-11 |  |

|           | 3.4.1 Location of setting jumpers                | 3-11 |  |

|           | 3.4.2 Factory default setting                    | 3-12 |  |

|           | 3.4.3 Master drive-slave drive setting           | 3-12 |  |

|           | 3.4.4 CSEL setting                               | 3-13 |  |

|           | 3.4.5 Power Up in Standby setting                | 3-14 |  |

| CHAPTER 4 | Theory of Device Operation                       | 4-1  |  |

|           | 4.1 Outline                                      | 4-2  |  |

|           | 4.2 Subassemblies                                | 4-2  |  |

|           | 4.2.1 Disk                                       | 4-2  |  |

|           | 4.2.2 Spindle                                    | 4-2  |  |

|           | 4.2.3 Actuator                                   | 4-2  |  |

|           | 4.2.4 Air filter                                 | 4-3  |  |

|           | 4.3 Circuit Configuration                        | 4-3  |  |

|           | 4.4 Power-on Sequence                            | 4-6  |  |

|           | 4.5 Self-calibration                             | 4-7  |  |

|           | 4.5.1 Self-calibration contents                  | 4-7  |  |

|           | 4.5.2 Execution timing of self-calibration       | 4-8  |  |

|           | 4.5.3 Command processing during self-calibration | 4-8  |  |

|           | 4.6 Read/write Circuit                           | 4-9  |  |

|           | 4.6.1 Read/write preamplifier (PreAMP)           | 4-9  |  |

x C141-E195-02EN

|           | 4.6.2 Write circuit                                      | 4-9   |

|-----------|----------------------------------------------------------|-------|

|           | 4.6.3 Read circuit                                       | 4-10  |

|           | 4.6.4 Digital PLL circuit                                | 4-11  |

|           | 4.7 Servo Control                                        | 4-12  |

|           | 4.7.1 Servo control circuit                              | 4-12  |

|           | 4.7.2 Data-surface servo format                          | 4-14  |

|           | 4.7.3 Servo frame format                                 | 4-16  |

|           | 4.7.4 Actuator motor control                             | 4-17  |

|           | 4.7.5 Spindle motor control                              | 4-18  |

| CHAPTER 5 | Interface                                                | 5-1   |

|           | 5.1 Physical Interface                                   | 5-2   |

|           | 5.1.1 Interface signals                                  | 5-2   |

|           | 5.1.2 Signal assignment on the connector                 | 5-3   |

|           | 5.2 Logical Interface                                    | 5-6   |

|           | 5.2.1 I/O registers                                      | 5-7   |

|           | 5.2.2 Command block registers                            | 5-8   |

|           | 5.2.3 Control block registers                            | 5-13  |

|           | 5.3 Host Commands                                        | 5-14  |

|           | 5.3.1 Command code and parameters                        | 5-14  |

|           | 5.3.2 Command descriptions                               | 5-18  |

|           | 5.3.3 Error posting                                      | 5-107 |

|           | 5.4 Command Protocol                                     | 5-109 |

|           | 5.4.1 PIO Data transferring commands from device to host | 5-109 |

|           | 5.4.2 PIO Data transferring commands from host to device | 5-112 |

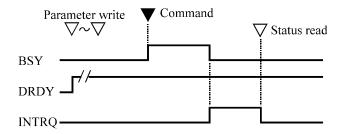

|           | 5.4.3 Commands without data transfer                     | 5-114 |

|           | 5.4.4 Other commands                                     | 5-115 |

|           | 5.4.5 DMA data transfer commands                         | 5-115 |

|           | 5.5 Ultra DMA Feature Set                                | 5-118 |

|           | 5.5.1 Overview                                           | 5-118 |

|           | 5.5.2 Phases of operation                                | 5-119 |

|           | 5.5.3 Ultra DMA data in commands                         | 5-119 |

|           | 5.5.3.1 Initiating an Ultra DMA data in burst           | 5-119 |

|-----------|---------------------------------------------------------|-------|

|           | 5.5.3.2 The data in transfer                            | 5-120 |

|           | 5.5.3.3 Pausing an Ultra DMA data in burst              | 5-120 |

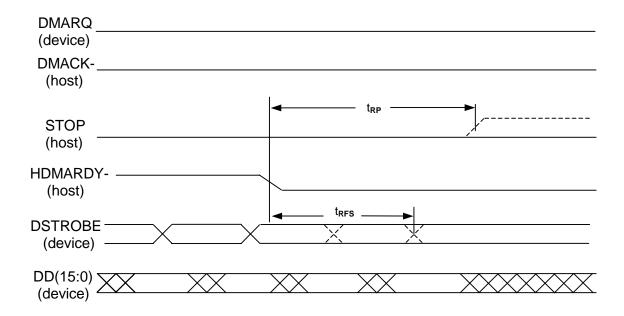

|           | 5.5.3.4 Terminating an Ultra DMA data in burst          | 5-121 |

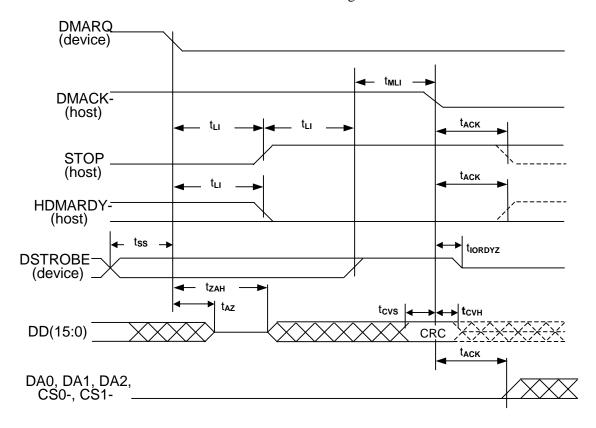

|           | 5.5.4 Ultra DMA data out commands                       | 5-124 |

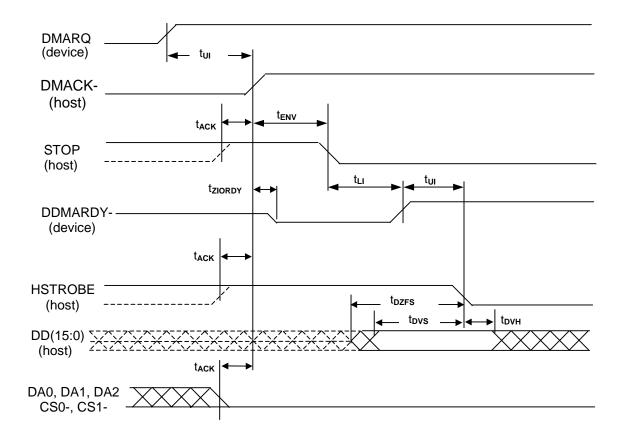

|           | 5.5.4.1 Initiating an Ultra DMA data out burst          | 5-124 |

|           | 5.5.4.2 The data out transfer                           | 5-124 |

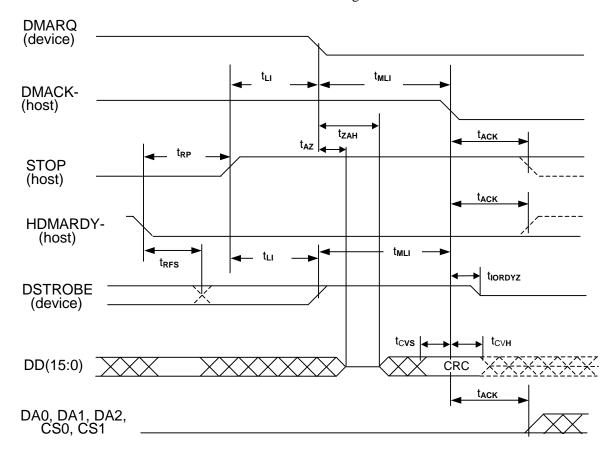

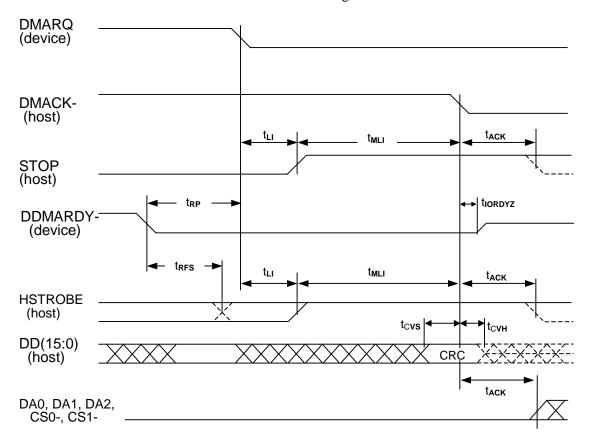

|           | 5.5.4.3 Pausing an Ultra DMA data out burst             | 5-125 |

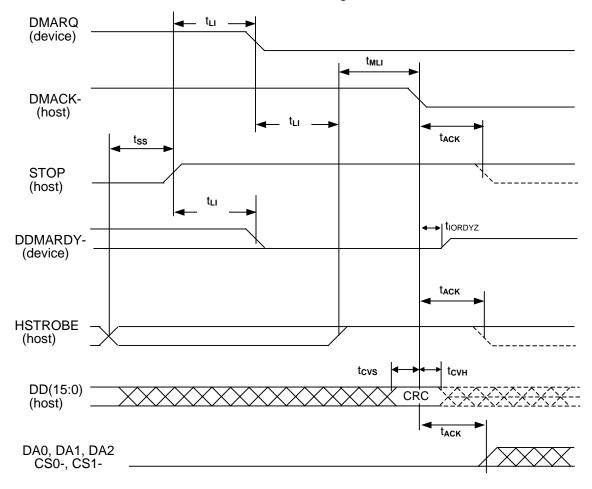

|           | 5.5.4.4 Terminating an Ultra DMA data out burst         | 5-126 |

|           | 5.5.5 Ultra DMA CRC rules                               | 5-128 |

|           | 5.5.6 Series termination required for Ultra DMA         | 5-129 |

|           | 5.6 Timing                                              | 5-130 |

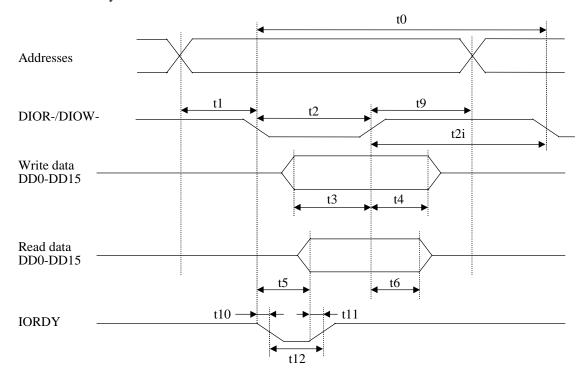

|           | 5.6.1 PIO data transfer                                 | 5-130 |

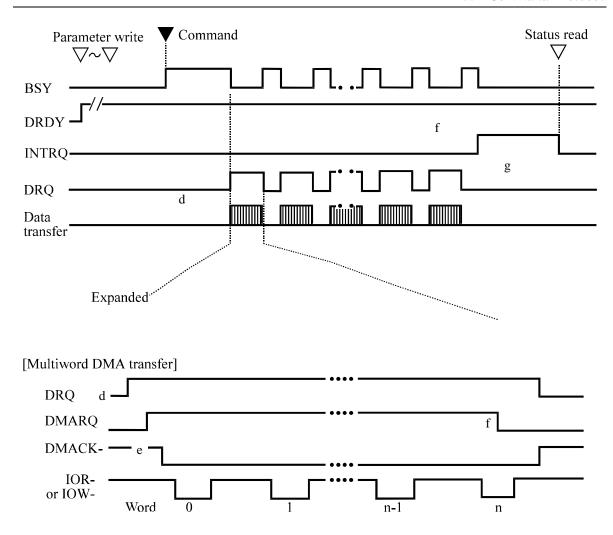

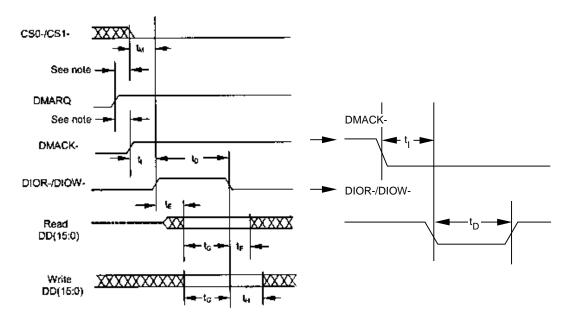

|           | 5.6.2 Multiword data transfer                           | 5-131 |

|           | 5.6.3 Ultra DMA data transfer                           | 5-132 |

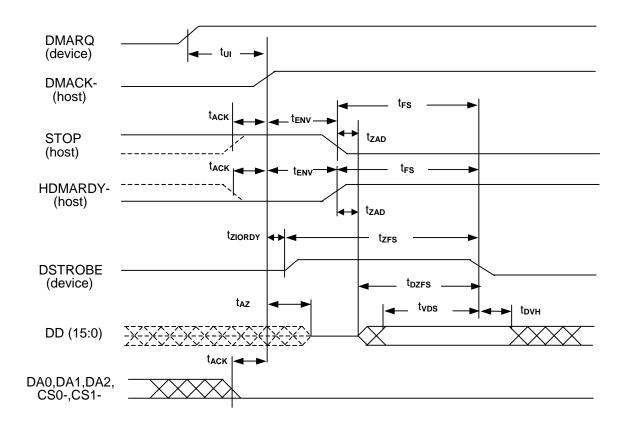

|           | 5.6.3.1 Initiating an Ultra DMA data in burst           | 5-132 |

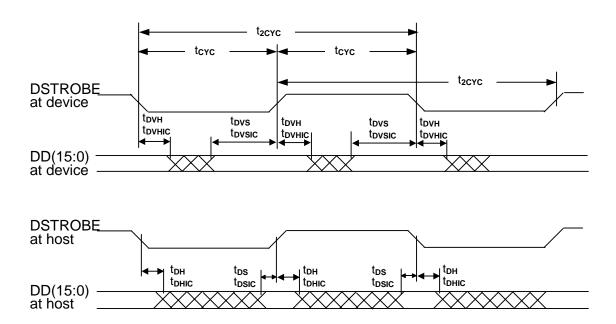

|           | 5.6.3.2 Ultra DMA data burst timing requirements        | 5-133 |

|           | 5.6.3.3 Sustained Ultra DMA data in burst               | 5-136 |

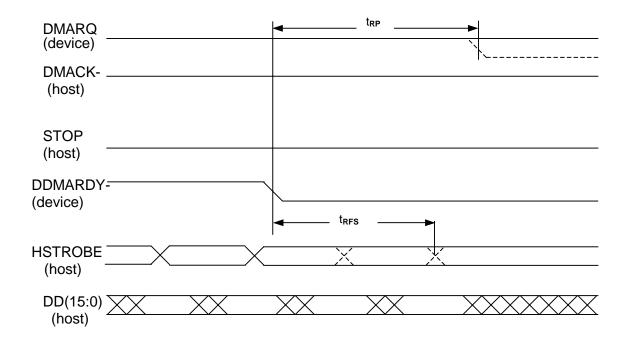

|           | 5.6.3.4 Host pausing an Ultra DMA data in burst         | 5-137 |

|           | 5.6.3.5 Device terminating an Ultra DMA data in burst   | 5-138 |

|           | 5.6.3.6 Host terminating an Ultra DMA data in burst     | 5-139 |

|           | 5.6.3.7 Initiating an Ultra DMA data out burst          | 5-140 |

|           | 5.6.3.8 Sustained Ultra DMA data out burst              | 5-141 |

|           | 5.6.3.9 Device pausing an Ultra DMA data out burst      | 5-142 |

|           | 5.6.3.10 Host terminating an Ultra DMA data out burst   | 5-143 |

|           | 5.6.3.11 Device terminating an Ultra DMA data out burst | 5-144 |

|           | 5.6.4 Power-on and reset                                | 5-145 |

| CHAPTER 6 | Operations                                              | 6-1   |

|           | 6.1 Device Response to the Reset                        | 6-2   |

|           | 6.1.1 Response to power-on                              | 6-2   |

|           | 6.1.2 Response to hardware reset                        | 6-3   |

|           | 6.1.3 Response to software reset                        | 6-5   |

|           | 6.1.4 Response to diagnostic command                    | 6-6   |

|           |                                                         |       |

xii C141-E195-02EN

| 6.2              | Power Save                                   | 6-7  |

|------------------|----------------------------------------------|------|

| 6.2.1            | Power save mode                              | 6-7  |

| 6.2.2            | Power commands                               | 6-9  |

| 6.3              | Defect Processing                            | 6-9  |

| 6.3.1            | Spare area                                   | 6-9  |

| 6.3.2            | Alternating processing for defective sectors | 6-10 |

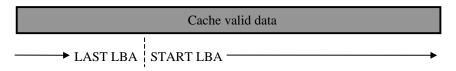

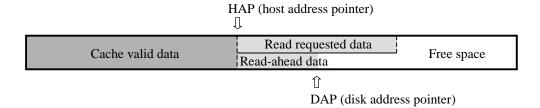

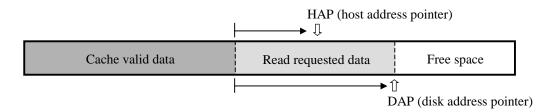

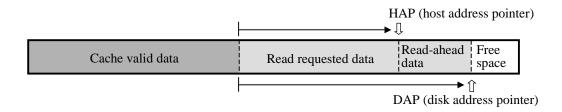

| 6.4              | Read-ahead Cache                             | 6-12 |

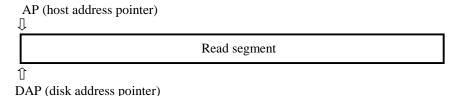

| 6.4.1            | DATA buffer structure                        | 6-12 |

| 6.4.2            | Caching operation                            | 6-13 |

| 6.4.3            | Using the read segment buffer                | 6-15 |

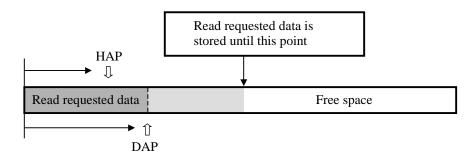

| 6.4.3.           | 1 Miss-hit                                   | 6-15 |

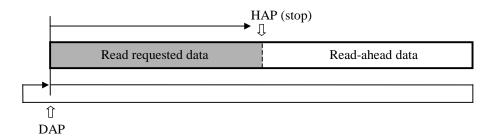

| 6.4.3.           | 2 Sequential Hit                             | 6-16 |

| 6.4.3.           | 3 Full hit                                   | 6-17 |

| 6.4.3.           | 4 Partial hit                                | 6-18 |

| 6.5              | Write Cache                                  | 6-19 |

| 6.5.1            | Cache operation                              | 6-19 |

| Glossary         |                                              | GL-1 |

| Acronyms and Abb | reviations                                   | AB-1 |

| Index            |                                              | IN-1 |

# Illustrations

# **Figures**

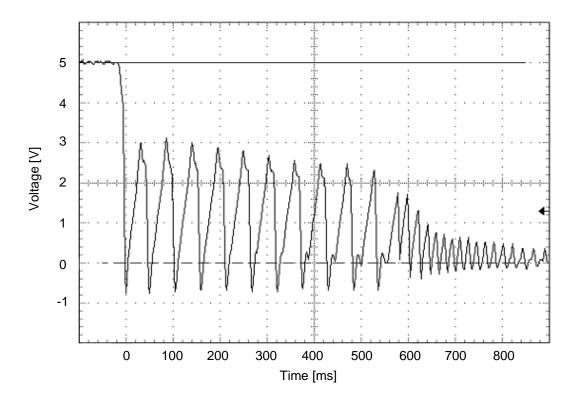

| Figure 1.1            | Negative voltage at +5 V when power is turned off             | 1-6  |

|-----------------------|---------------------------------------------------------------|------|

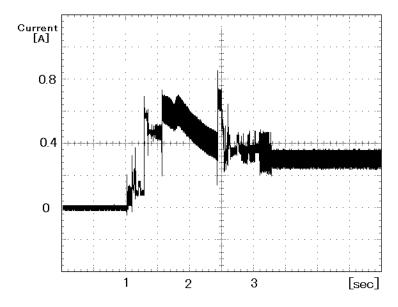

| Figure 1.2            | Current fluctuation (Typ.) at $+5\ V$ when power is turned on | 1-8  |

| Figure 2.1            | Disk drive outerview                                          | 2.2  |

| Figure 2.1 Figure 2.2 | 1 drive system configuration                                  |      |

| Figure 2.2 Figure 2.3 | 2 drives configuration                                        |      |

| riguie 2.3            | 2 drives configuration                                        | 2-4  |

| Figure 3.1            | Dimensions                                                    | 3-2  |

| Figure 3.2            | Orientation                                                   | 3-3  |

| Figure 3.3            | Mounting frame structure                                      | 3-4  |

| Figure 3.4            | Location of breather                                          | 3-5  |

| Figure 3.5            | Surface temperature measurement points                        | 3-6  |

| Figure 3.6            | Service area                                                  | 3-7  |

| Figure 3.7            | Handling cautions                                             | 3-8  |

| Figure 3.8            | Connector locations                                           | 3-9  |

| Figure 3.9            | Cable connections                                             | 3-10 |

| Figure 3.10           | Power supply connector pins (CN1)                             | 3-11 |

| Figure 3.11           | Jumper location                                               | 3-11 |

| Figure 3.12           | Factory default setting                                       | 3-12 |

| Figure 3.13           | Jumper setting of master or slave drive                       | 3-12 |

| Figure 3.14           | CSEL setting                                                  | 3-13 |

| Figure 3.15           | Example (1) of Cable Select                                   | 3-13 |

| Figure 3.16           | Example (2) of Cable Select                                   | 3-14 |

| Figure 4.1            | Decree Consider Configuration                                 | 4 4  |

| Figure 4.1            | Power Supply Configuration                                    |      |

| Figure 4.2            | Circuit Configuration                                         |      |

| Figure 4.3            | Power-on operation sequence                                   |      |

| Figure 4.4            | Read/write circuit block diagram                              |      |

| Figure 4.5            | Frequency characteristic of programmable filter               |      |

| Figure 4.6            | Block diagram of servo control circuit                        |      |

| Figure 4.7            | Physical sector servo configuration on disk surface           |      |

| Figure 4.8            | Servo frame format                                            | 4-10 |

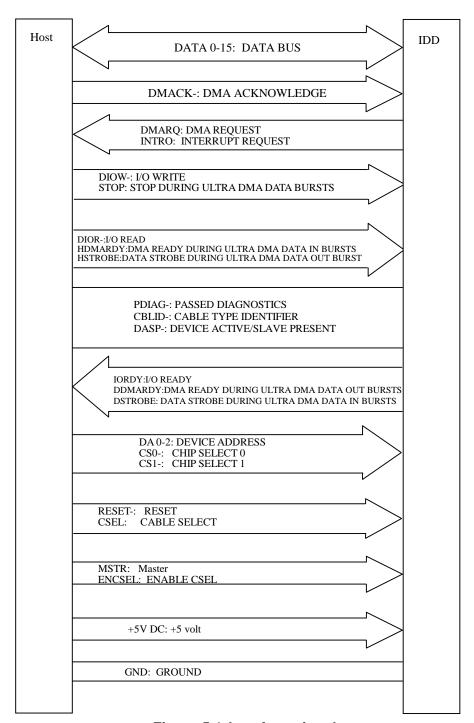

| Figure 5.1            | Interface signals                                             | 5-2  |

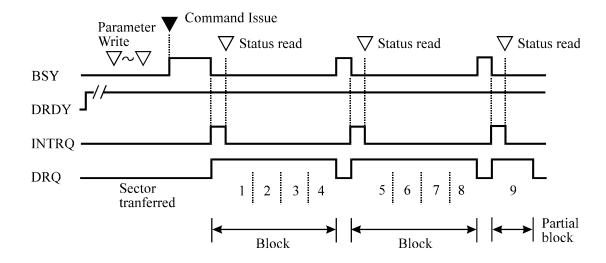

| Figure 5.2            | Execution example of READ MULTIPLE command                    |      |

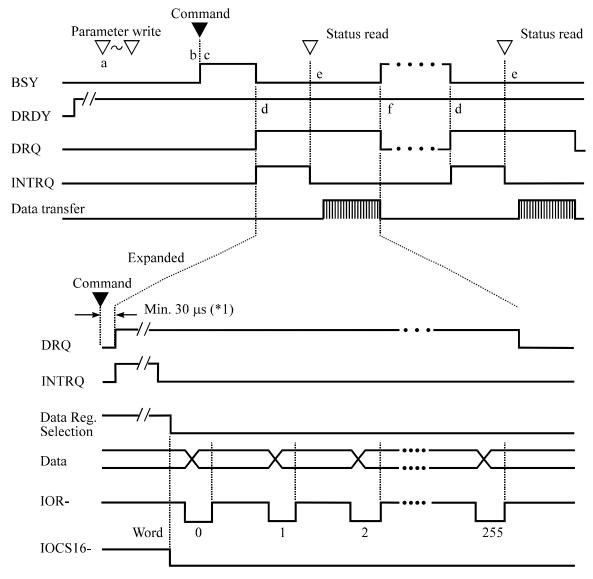

| Figure 5.3            | Read Sector(s) command protocol                               |      |

|                       |                                                               |      |

xiv C141-E195-02EN

| Figure 5.4  | Protocol for command abort                               | 5-111 |

|-------------|----------------------------------------------------------|-------|

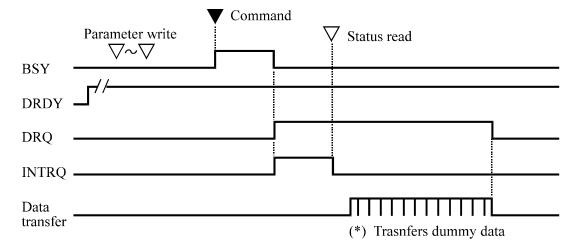

| Figure 5.5  | WRITE SECTOR(S) command protocol                         | 5-113 |

| Figure 5.6  | Protocol for the command execution without data transfer | 5-114 |

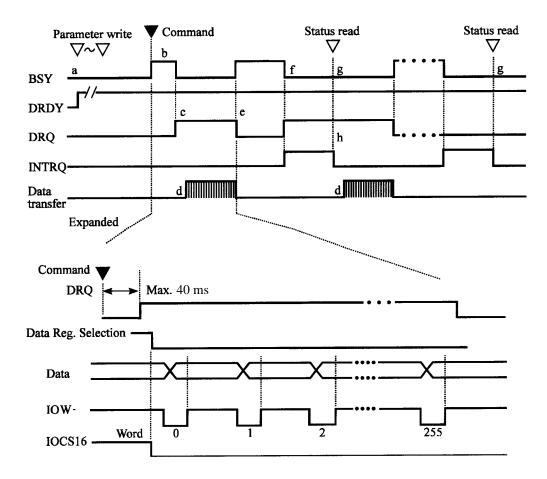

| Figure 5.7  | Normal DMA data transfer                                 | 5-117 |

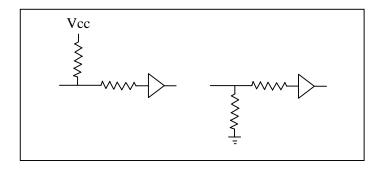

| Figure 5.8  | Ultra DMA termination with pull-up or pull-down          | 5-129 |

| Figure 5.9  | PIO data transfer timing                                 | 5-130 |

| Figure 5.10 | Multiword DMA data transfer timing (mode 2)              | 5-131 |

| Figure 5.11 | Initiating an Ultra DMA data in burst                    | 5-132 |

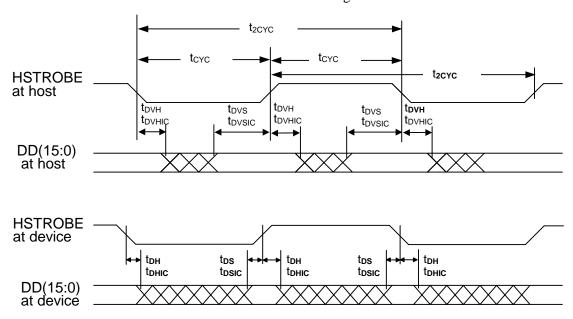

| Figure 5.12 | Sustained Ultra DMA data in burst                        | 5-136 |

| Figure 5.13 | Host pausing an Ultra DMA data in burst                  | 5-137 |

| Figure 5.14 | Device terminating an Ultra DMA data in burst            | 5-138 |

| Figure 5.15 | Host terminating an Ultra DMA data in burst              | 5-139 |

| Figure 5.16 | Initiating an Ultra DMA data out burst                   | 5-140 |

| Figure 5.17 | Sustained Ultra DMA data out burst                       | 5-141 |

| Figure 5.18 | Device pausing an Ultra DMA data out burst               | 5-142 |

| Figure 5.19 | Host terminating an Ultra DMA data out burst             | 5-143 |

| Figure 5.20 | Device terminating an Ultra DMA data out burst           | 5-144 |

| Figure 5.21 | Power-on Reset Timing                                    | 5-145 |

| Figure 6.1  | Response to power-on                                     | 6-3   |

| Figure 6.2  | Response to hardware reset                               |       |

| Figure 6.3  | Response to software reset                               |       |

| Figure 6.4  | Response to diagnostic command                           |       |

| Figure 6.5  | Sector slip processing                                   |       |

| Figure 6.6  | Automatic alternating processing                         |       |

| Figure 6.7  | Data buffer structure                                    |       |

C141-E195-02EN xv

## **Tables**

| Table 1.1   | Specifications                                                                | 1-4   |

|-------------|-------------------------------------------------------------------------------|-------|

| Table 1.2   | Model names and product numbers                                               | 1-5   |

| Table 1.3   | Current and power dissipation                                                 | 1-7   |

| Table 1.4   | Environmental specifications                                                  | 1-8   |

| Table 1.5   | Acoustic noise specification                                                  | 1-9   |

| Table 1.6   | Shock and vibration specification                                             | 1-9   |

|             |                                                                               |       |

| Table 3.1   | Surface temperature measurement points and standard values                    | 3-6   |

| Table 3.2   | Cable connector specifications.                                               | 3-10  |

|             |                                                                               |       |

| Table 5.1   | Signal assignment on the interface connector                                  | 5-3   |

| Table 5.2   | I/O registers                                                                 | 5-7   |

| Table 5.3   | Command code and parameters                                                   |       |

| Table 5.4   | Information to be read by IDENTIFY DEVICE command                             | 5-34  |

| Table 5.5   | Features register values and settable modes                                   | 5-44  |

| Table 5.6   | Diagnostic code                                                               | 5-56  |

| Table 5.7   | Features Register values (subcommands) and functions                          | 5-68  |

| Table 5.8   | Format of device attribute value data                                         | 5-72  |

| Table 5.9   | Format of insurance failure threshold value data                              | 5-72  |

| Table 5.10  | Log Directory Data Format                                                     | 5-77  |

| Table 5.11  | Data format of SMART Summary Error Log                                        | 5-78  |

| Table 5.11. | 1 Data format of SMART Comprehensive Error Log                                | 5-79  |

| Table 5.12  | SMART self-test log data format                                               | 5-80  |

| Table 5.13  | Selective self-test log data structure                                        | 5-81  |

| Table 5.14  | Selective self-test feature flags                                             | 5-82  |

| Table 5.15  | Contents of security password                                                 | 5-83  |

| Table 5.16  | Contents of SECURITY SET PASSWORD data                                        | 5-87  |

| Table 5.17  | Relationship between combination of Identifier                                |       |

|             | and Security level, and operation of the lock function                        | 5-88  |

| Table 5.18  | DEVICE CONFIGURATION IDENTIFY data structure                                  | 5-94  |

| Table 5.19  | Operation of DOWNLOAD MICRO CODE                                              | 5-106 |

| Table 5.20  | Example of rewriting procedure of data 384 KBytes (30000h Bytes) of microcode | 5-106 |

| Table 5.21  | Command code and parameters                                                   | 5-107 |

| Table 5.22  | Recommended series termination for Ultra DMA                                  | 5-129 |

| Table 5.23  | Ultra DMA data burst timing requirements                                      | 5-133 |

| Table 5.24  | Ultra DMA sender and recipient timing requirements                            | 5-135 |

xvi C141-E195-02EN

# **CHAPTER 1 Device Overview**

1.1 **Features** 1.2 **Device Specifications** 1.3 **Power Requirements Environmental Specifications** 1.4 Acoustic Noise 1.5 1.6 Shock and Vibration 1.7 Reliability Error Rate 1.8 1.9 Media Defects Load/Unload Function 1.10 1.11 Advanced Power Management

Overview and features are described in this chapter, and specifications and power requirement are described.

The disk drive is 2.5-inch hard disk drive with built-in disk controllers. These disk drives use the AT-bus hard disk interface protocol and are compact and reliable.

#### 1.1 Features

#### 1.1.1 Functions and performance

The following features of the disk drive is described.

#### (1) Compact

The disk drive has 1 disk or 2 disks of 65 mm (2.5 inches) diameter, and its height is 9.5 mm (0.374 inch).

#### (2) Large capacity

The disk drive can record up to 40 GB (formatted) on one disk using the 60/63 RLL recording method and 30 recording zone technology. The disk drive has a formatted capacity of 80 GB (MHT2080AH), 60 GB (MHT2060AH), and 40 GB (MHT2040AH) respectively.

#### (3) High-speed Transfer rate

The disk drives have an internal data rate up to 55.4 MB/s. The disk drive supports an external data rate up to 100 MB/s (U-DMA mode 5).

#### (4) Average positioning time

Use of a rotary voice coil motor in the head positioning mechanism greatly increases the positioning speed. The average positioning time is 12 ms (at read).

#### 1.1.2 Adaptability

#### (1) Power save mode

The power save mode feature for idle operation, stand by and sleep modes makes The disk drives ideal for applications where power consumption is a factor.

#### (2) Wide temperature range

The disk drives can be used over a wide temperature range  $(5 \, ^{\circ}\text{C} \text{ to } 55 \, ^{\circ}\text{C})$ .

#### (3) Low noise and vibration

In Ready status, the noise of the disk drives is only 25 dBA (measured at 0.3 m apart from the drive under the idle mode).

#### (4) High resistance against shock

The Load/Unload mechanism is highly resistant against non-operation shock up to  $8820~\text{m/s}^2$  (900G).

1-2 C141-E195-02EN

#### 1.1.3 Interface

#### (1) Connection to ATA interface

The disk drives have built-in controllers compatible with the ATA interface.

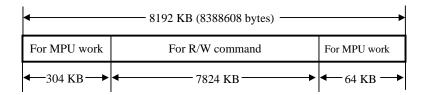

#### (2) 8 MB data buffer

The disk drives use a 8 MB data buffer to transfer data between the host and the disk media.

In combination with the read-ahead cache system described in item (3) and the write cache described in item (7), the buffer contributes to efficient I/O processing.

#### (3) Read-ahead cache system

After the execution of a disk read command, the disk drive automatically reads the subsequent data block and writes it to the data buffer (read ahead operation). This cache system enables fast data access. The next disk read command would normally cause another disk access. But, if the read ahead data corresponds to the data requested by the next read command, the data in the buffer can be transferred instead.

#### (4) Master/slave

The disk drives can be connected to ATA interface as daisy chain configuration. Drive 0 is a master device, drive 1 is a slave device.

#### (5) Error correction and retry by ECC

If a recoverable error occurs, the disk drives themselves attempt error recovery. The ECC has improved buffer error correction for correctable data errors.

#### (6) Self-diagnosis

The disk drives have a diagnostic function to check operation of the controller and disk drives. Executing a diagnostic function of the smart command invokes self-diagnosis.

#### (7) Write cache

When the disk drives receive a write command, the disk drives post the command completion at completion of transferring data to the data buffer completion of writing to the disk media. This feature reduces the access time at writing.

# 1.2 Device Specifications

# 1.2.1 Specifications summary

Table 1.1 shows the specifications of the disk drives.

Table 1.1 Specifications (1/2)

|                                                 | MHT2080AH                                                                       | MHT2060AH   | MHT2040AH  |  |

|-------------------------------------------------|---------------------------------------------------------------------------------|-------------|------------|--|

| Format Capacity (*1)                            | 80 GB                                                                           | 60 GB       | 40 GB      |  |

| Number of Sectors (User)                        | 156,301,488                                                                     | 117,210,240 | 78,140,160 |  |

| Bytes per Sector                                | 512                                                                             |             |            |  |

| Rotational Speed                                | 5,400 rpm ± 1%                                                                  |             |            |  |

| Average Latency                                 |                                                                                 | 5.56 ms     |            |  |

| Positioning time (read and seek)                |                                                                                 |             |            |  |

| Minimum (Track-Track)                           | 1.5 ms (typ.)                                                                   |             |            |  |

| Average                                         | Read: 12ms (typ.)                                                               |             |            |  |

| Maximum (Full)                                  | 22 ms (typ.)                                                                    |             |            |  |

| Start time                                      | 4.0 sec (typ.)                                                                  |             |            |  |

| Interface                                       | ATA-6 (Max. Cable length: 18inches (0.46 m)) (equipped with expansion function) |             |            |  |

| Data Transfer Rate                              |                                                                                 |             |            |  |

| To/From Media                                   | 55.4 MB/s Max.                                                                  |             |            |  |

| To/From Host                                    | 100 MB/s Max (U-DMA mode5)                                                      |             |            |  |

| Data Buffer Size                                | 4 MB                                                                            |             |            |  |

| Physical Dimensions<br>(Height × Width × Depth) | 9.5 mm × 100.0 mm × 70.0 mm                                                     |             |            |  |

| Weight                                          |                                                                                 | 99 g (max)  |            |  |

<sup>\*1:</sup> Capacity under the LBA mode.

1-4 C141-E195-02EN

Table 1.1 lists the formatted capacity, number of logical cylinders, number of heads, and number of sectors of every model for which the CHS mode has been selected using the BIOS setup utility on the host.

Table 1.1 Specifications (2/2)

| Model     | Capacity (*1) | No. of Cylinder | No. of Heads | No. of Sectors |

|-----------|---------------|-----------------|--------------|----------------|

| MHT2080AH | 8.45 GB       | 16,383          | 16           | 63             |

| MHT2060AH | 8.45 GB       | 16,383          | 16           | 63             |

| MHT2040AH | 8.45 GB       | 16,383          | 16           | 63             |

<sup>\*1</sup> On using for the units of BIOS parameter.

#### 1.2.2 Model and product number

Table 1.2 lists the model names and product numbers of the disk drive.

Table 1.2 Model names and product numbers

| Model Name | Capacity (user area) | Mounting screw | Order No.           |

|------------|----------------------|----------------|---------------------|

| MHT2080AH  | 80 GB                | M3 depth 3     | CA06377-B048        |

| MHT2060AH  | 60 GB                | M3 depth 3     | CA06377-B046        |

| MHT2040AH  | 40 GB                | M3 depth 3     | CA06377-B024/(B034) |

# 1.3 Power Requirements

(1) Input Voltage

$\bullet$  + 5 V  $\pm$  5 %

(2) Ripple

|           | +5 V                  |  |

|-----------|-----------------------|--|

| Maximum   | 100 mV (peak to peak) |  |

| Frequency | DC to 1 MHz           |  |

(3) A negative voltage like the bottom figure isn't to occur at +5 V when power is turned off and, a thing with no ringing.

Permissible level: -0.2 V

Figure 1.1 Negative voltage at +5 V when power is turned off

1-6 C141-E195-02EN

#### (4) Current Requirements and Power Dissipation

Table 1.3 lists the current and power dissipation (typical).

Table 1.3 Current and power dissipation

|                           | Typical RMS Current                                                                               | Typical Power (*3)       |  |

|---------------------------|---------------------------------------------------------------------------------------------------|--------------------------|--|

| Spin up (*1)              | 1.0 A                                                                                             | 5.0 W                    |  |

| Idle                      | 170 mA                                                                                            | 0.85 W                   |  |

| R/W (on track) (*2)       | Read 460 mA / Write 460mA                                                                         | Read 2.3 W / Write 2.3 W |  |

| Seek (*5)                 | 500 mA                                                                                            | 2.5 W                    |  |

| Standby                   | 50 mA                                                                                             | 0.25 W                   |  |

| Sleep                     | 20 mA                                                                                             | 0.1 W                    |  |

| Energy<br>Efficiency (*4) | — MHT2080AH (CA06377-B048): rank E 0.011W/GB MHT2060AH (CA06377-B046) : rank E 0.014 W/GB         |                          |  |

|                           | MHT2040AH (CA06377-B034)<br>: rank E 0.021W/GB<br>MHT2040AH (CA06377-B024)<br>: rank D 0.021 W/GB |                          |  |

- \*1 Current at starting spindle motor.

- \*2 Current and power level when the operation (command) that accompanies a transfer of 63 sectors is executed 3 times in 100 ms

- \*3 Power requirements reflect nominal values for +5 V power.

- \*4 Energy efficiency based on the Law concerning the Rational Use of Energy indicates the value obtained by dividing power consumption by the storage capacity. (Japan only)

- \*5 The seek average current is specified based on three operations per 100 msec.

- (5) Current fluctuation (Typ.) at +5 V when power is turned on

Figure 1.2 Current fluctuation (Typ.) at +5 V when power is turned on

#### (6) Power on/off sequence

The voltage detector circuits monitor +5 V. The circuits do not allow a write signal if either voltage is abnormal. These prevent data from being destroyed and eliminates the need to be concerned with the power on/off sequence.

# 1.4 Environmental Specifications

Table 1.4 lists the environmental specifications.

**Table 1.4 Environmental specifications**

| Item                             | Specification                              |  |

|----------------------------------|--------------------------------------------|--|

| Temperature                      |                                            |  |

| Operating                        | 5 °C to 55 °C (ambient)                    |  |

|                                  | 5 °C to 60 °C (disk enclosure surface)     |  |

| Non-operating                    | –40 °C to 65 °C                            |  |

| Thermal Gradient                 | 20 °C/h or less                            |  |

| Humidity                         |                                            |  |

| Operating                        | 8 % to 90 % RH (Non-condensing)            |  |

| Non-operating                    | 5 % to 95 % RH (Non-condensing)            |  |

| Maximum Wet Bulb                 | 29 °C (Operating)<br>40 °C (Non-operating) |  |

| Altitude (relative to sea level) | 1 0/                                       |  |

| Operating                        | -300 to 3,000 m                            |  |

| Non-operating                    | -300 to 12,000 m                           |  |

1-8 C141-E195-02EN

## 1.5 Acoustic Noise

Table 1.5 lists the acoustic noise specification.

Table 1.5 Acoustic noise specification

| Item |                          | Specification (typ.)                          |  |

|------|--------------------------|-----------------------------------------------|--|

| •    | Idle mode (DRIVE READY)  | 2.2 B [MHT2040AH]                             |  |

|      | Sound Power              | 2.8 B [MHT2080AH/MHT2060AH/MHT2040AH (*1)]    |  |

|      | Sound Pressure (at 0.3m) | 25 dB(A) [MHT2040AH]                          |  |

|      |                          | 34 dB(A) [MHT2080AH/MHT2060AH/MHT2040AH (*1)] |  |

<sup>\* 1</sup> In case of model "CA06377-B034".

## 1.6 Shock and Vibration

Table 1.6 lists the shock and vibration specification.

Table 1.6 Shock and vibration specification

| Item                                              | Specification                                                                                |  |

|---------------------------------------------------|----------------------------------------------------------------------------------------------|--|

| Vibration (Swept sine, 1/4 octave per minute)     |                                                                                              |  |

| Operating                                         | 5 to 500 Hz, 9.8m/s <sup>2</sup> 0-peak (1G 0-peak) (without non-recovered errors)           |  |

| Non-operating                                     | 5 to 500 Hz, 49m/s <sup>2</sup> 0-peak (5G 0-peak) (no damage)                               |  |

| Shock (half-sine pulse)                           |                                                                                              |  |

| <ul><li>Operating</li><li>Non-operating</li></ul> | 2207 m/s <sup>2</sup> 0-peak (225G 0-peak)<br>2ms duration<br>(without non-recovered errors) |  |

|                                                   | 8820 m/s <sup>2</sup> 0-peak (900G 0-peak)<br>1ms duration                                   |  |

|                                                   | 1176 m/s <sup>2</sup> 0-peak (120G 0-peak)<br>11ms duration                                  |  |

|                                                   | (no damage)                                                                                  |  |

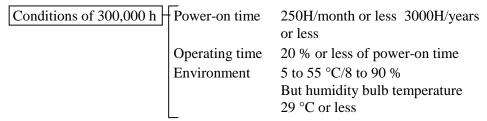

## 1.7 Reliability

#### (1) Mean time between failures (MTBF)

MTBF is defined as follows:

\*1 "Disk drive defects" refers to defects that involve repair, readjustment, or replacement. Disk drive defects do not include failures caused by external factors, such as damage caused by handling, inappropriate operating environments, defects in the power supply host system, or interface cable.

#### (2) Mean time to repair (MTTR)

The mean time to repair (MTTR) is 30 minutes or less, if repaired by a specialist maintenance staff member.

#### (3) Service life

In situations where management and handling are correct, the disk drive requires no overhaul for five years when the DE surface temperature is less than 48 °C. When the DE surface temperature exceeds 48 °C, the disk drives requires no overhaul for five years or 20,000 hours of operation, whichever occurs first. Refer to item (3) in Subsection 3.2 for the measurement point of the DE surface temperature. Also the operating conditions except the environment temperature are based on the MTBF conditions.

#### (4) Data assurance in the event of power failure

Except for the data block being written to, the data on the disk media is assured in the event of any power supply abnormalities. This does not include power supply abnormalities during disk media initialization (formatting) or processing of defects (alternative block assignment).

1-10 C141-E195-02EN

#### 1.8 Error Rate

Known defects, for which alternative blocks can be assigned, are not included in the error rate count below. It is assumed that the data blocks to be accessed are evenly distributed on the disk media.

#### (1) Unrecoverable read error

Read errors that cannot be recovered by maximum read retries of drive without user's retry and ECC corrections shall occur no more than 10 times when reading data of 10<sup>14</sup> bits. Read retries are executed according to the disk drive's error recovery procedure, and include read retries accompanying head offset operations.

#### (2) Positioning error

Positioning (seek) errors that can be recovered by one retry shall occur no more than 10 times in  $10^7$  seek operations.

#### 1.9 Media Defects

Defective sectors are replaced with alternates when the disk are formatted prior to shipment from the factory (low level format). Thus, the hosts see a defect-free devices.

Alternate sectors are automatically accessed by the disk drive. The user need not be concerned with access to alternate sectors.

#### 1.10Load/Unload Function

The Load/Unload function is a mechanism that loads the head on the disk and unloads the head from the disk.

The product supports a minimum of 300,000 normal Load/Unload cycles. Normal Unload is a normal head unloading operation and the commands listed below are executed.

- Hard Reset

- Standby

- Standby immediate

- Sleep

- Idle

Emergency Unload other than Normal Unload is performed when the power is shut down while the heads are still loaded on the disk.

The product supports the Emergency Unload a minimum of 20,000 times. When the power is shut down, the controlled Normal Unload cannot be executed. Therefore, the number of Emergency other than Normal Unload is specified.

#### Remark:

We recommend cutting the power supply of the HDD for this device after the Head Unload operation completes. The recommended power supply cutting sequence for this device is as follows:

1) Disk Flush

Flush Cache command execution.

2) Head Unload

Standby Immediate command execution.

3) Wait Status

Checking whether bit 7 of the status register was set to '0'. (wait to complete STANDBY IMMEDIATE command)

4) HDD power supply cutting

## 1.11 Advanced Power Management

The disk drive shifts to the three kinds of APM modes automatically under the Idle condition.

The APM mode can be chosen with a Sector Count register of the SET FEATURES(EF) command.

In APM Mode-1, which is the APM default mode, the operation status shifts till it finally reaches "Low Power Idle."

The disk drive complies with the three kinds of APM modes that a command from the host is required.

FR = 05h: Enable APM

$SC = C0h - FEh : Mode-0 Active Idle \rightarrow Low Power Idle$

$SC = 80h \text{ - BFh} \; : \quad \text{Mode-1 Active Idle} \to Low \; \text{Power Idle} \; (\text{Default})$

SC = 01h - 7Fh: Mode-2 Active Idle  $\rightarrow$  Low Power Idle  $\rightarrow$  Standby

FR = 85h: Disable APM (return to Default.)

1-12 C141-E195-02EN

Active Idle: The head is in a position of extreme inner in disk medium.

(VCM Lock)

Low Power Idle: The head is unloaded from disk. (VCM Unload)

The spindle motor rotates.

Standby: The spindle motor stops.

| APM Mode | Active Idle<br>(VCM Lock) | Low Power Idle<br>(VCM Unload) | Standby<br>(Spin Off) |

|----------|---------------------------|--------------------------------|-----------------------|

| Mode-0   | 0.2-1.2 sec               | 15 min.                        | N/A                   |

| Mode-1   | 0.2-1.2 sec               | 10.0-40.0 sec                  | N/A                   |

| Mode-2   | 0.2-1.2 sec               | 10.0-40.0 sec                  | 10.0-40.0 sec         |

When the maximum time that the HDD is waiting for commands has been exceeded:

Mode-0: Mode shifts from Active condition to Active Idle in 0.2-1.2, and to Low Power Idle in 15 minutes.

Mode-1: Mode shifts from Active condition to Active Idle in 0.2-1.2 seconds and to Low Power Idle in 10.0-40.0 seconds.

Mode-2: Mode shifts from Active condition to Active Idle in 0.2-1.2 seconds and to Low Power Idle in 10.0-40.0 seconds. After 10.0-40.0 seconds in Low Power Idle, the mode shifts to standby.

# **CHAPTER 2 Device Configuration**

- 2.1 Device Configuration

- 2.2 System Configuration

This chapter describes the internal configurations of the hard disk drives and the configuration of the systems in which they operate.

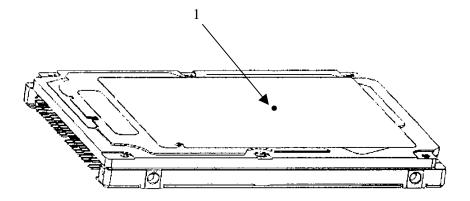

## 2.1 Device Configuration

Figure 2.1 shows the disk drive. The disk drive consists of a disk enclosure (DE), read/write preamplifier, and controller PCA. The disk enclosure contains the disk media, heads, spindle motors, actuators, and a circulating air filter.

Figure 2.1 Disk drive outerview

(1) Disk

The outer diameter of the disk is 65 mm. The inner diameter is 20 mm.

(2) Head

The heads are of the load/unload (L/UL) type. The head unloads the disk out of while the disk is not rotating and loads on the disk when the disk starts.

(3) Spindle motor

The disks are rotated by a direct drive Sensor-less DC motor.

(4) Actuator

The actuator uses a revolving voice coil motor (VCM) structure which consumes low power and generates very little heat. The head assembly at the edge of the actuator arm is controlled and positioned by feedback of the servo information read by the read/write head. If the power is not on or if the spindle motor is stopped, the head assembly stays on the ramp out of the disk and is fixed by a mechanical lock.

(5) Air circulation system

The disk enclosure (DE) is sealed to prevent dust and dirt from entering. The disk enclosure features a closed loop air circulation system that relies on the blower effect of the rotating disk. This system continuously circulates the air through the circulation filter to maintain the cleanliness of the air within the disk enclosure.

2-2 C141-E195-02EN

## (6) Read/write circuit

The read/write circuit uses a LSI chip for the read/write preamplifier. It improves data reliability by preventing errors caused by external noise.

#### (7) Controller circuit

The controller circuit consists of an LSI chip to improve reliability. The high-speed microprocessor unit (MPU) achieves a high-performance AT controller.

# 2.2 System Configuration

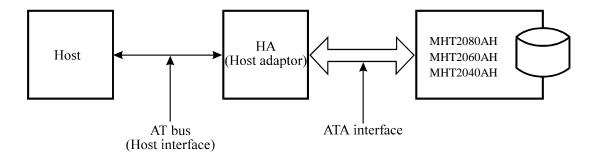

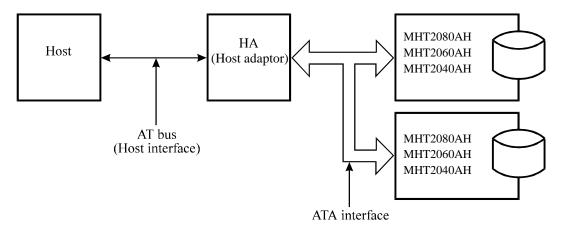

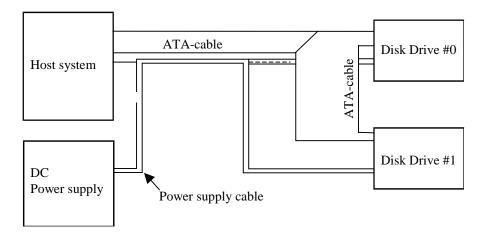

## 2.2.1 ATA interface

Figures 2.2 and 2.3 show the ATA interface system configuration. The drive has a 44pin PC AT interface connector and supports PIO mode 4 transfer at 16.6 MB/s, Multiword DMA mode 2 transfer at 16.6 MB/s and also U-DMA mode 5 (100 MB/s).

## 2.2.2 1 drive connection

Figure 2.2 1 drive system configuration

#### 2.2.3 2 drives connection

Note:

When the drive that is not conformed to ATA is connected to the disk drive above configuration, the operation is not guaranteed.

Figure 2.3 2 drives configuration

#### **IMPORTANT**

HA (host adaptor) consists of address decoder, driver, and receiver. ATA is an abbreviation of "AT attachment". The disk drive is conformed to the ATA-6 interface.

At high speed data transfer (PIO mode 4 or DMA mode 2 U-DMA mode 5), occurrence of ringing or crosstalk of the signal lines (AT bus) between the HA and the disk drive may be a great cause of the obstruction of system reliability. Thus, it is necessary that the capacitance of the signal lines including the HA and cable does not exceed the ATA-6 standard, and the cable length between the HA and the disk drive should be as short as possible.

No need to push the top cover of the disk drive. If the over-power worked, the cover could be contacted with the spindle motor. Thus, that could be made it the cause of failure.

2-4 C141-E195-02EN

# **CHAPTER 3 Installation Conditions**

3.1 Dimensions

3.2 Mounting

3.3 Cable Connections

3.4 Jumper Settings

This chapter gives the external dimensions, installation conditions, surface temperature conditions, cable connections, and switch settings of the hard disk drives.

For information about handling this hard disk drive and the system installation procedure, refer to the following Integration Guide. C141-E144

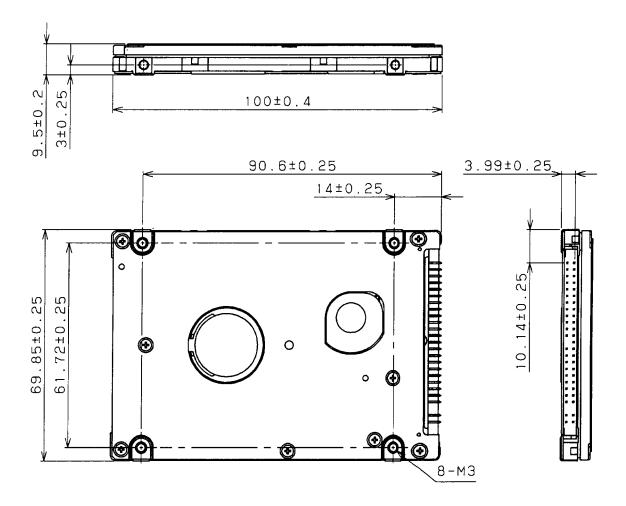

# 3.1 Dimensions

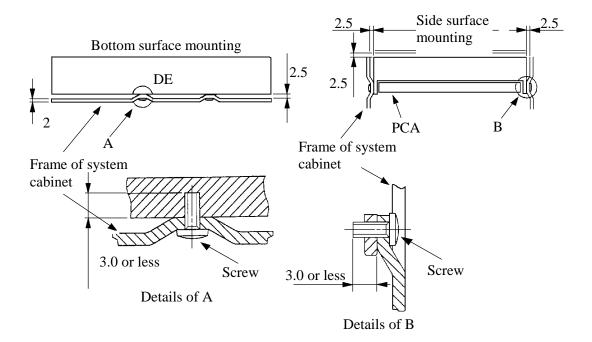

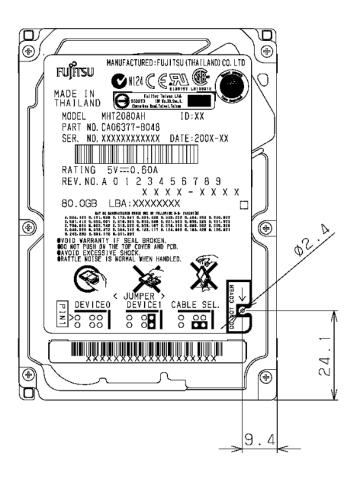

Figure 3.1 illustrates the dimensions of the disk drive and positions of the mounting screw holes. All dimensions are in mm.

Figure 3.1 Dimensions

3-2 C141-E195-02EN

# 3.2 Mounting

For information on mounting, see the "FUJITSU 2.5-INCH HDD INTEGRATION GUIDANCE (C141-E144)."

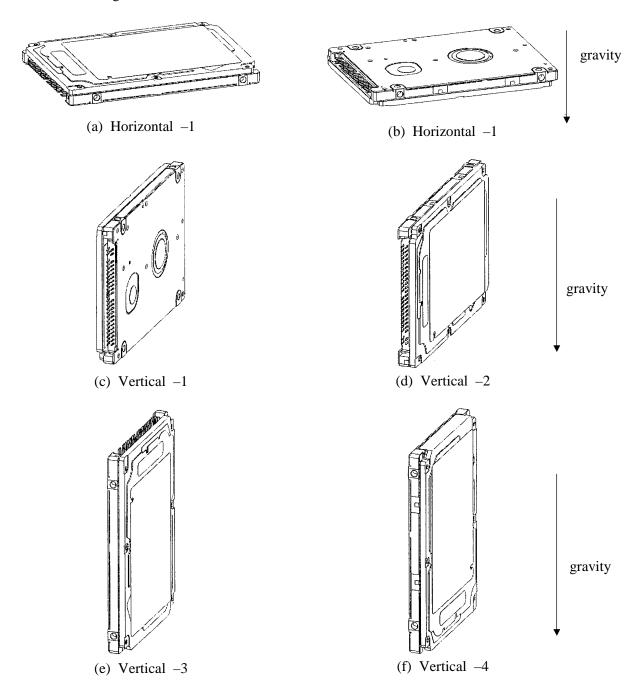

# (1) Orientation

Figure 3.2 illustrates the allowable orientations for the disk drive.

Figure 3.2 Orientation

## (2) Frame

The MR head bias of the HDD disk enclosure (DE) is zero. The mounting frame is connected to SG.

#### **IMPORTANT**

Use M3 screw for the mounting screw and the screw length should satisfy the specification in Figure 3.3.

The tightening torque must be 0.49N·m (5kgf·cm).

When attaching the HDD to the system frame, do not allow the system frame to touch parts (cover and base) other than parts to which the HDD is attached.

# (3) Limitation of mounting

Note) These dimensions are recommended values; if it is not possible to satisfy them, contact us.

Figure 3.3 Mounting frame structure

3-4 C141-E195-02EN

## **IMPORTANT**

Because of breather hole mounted to the HDD, do not allow this to close during mounting.

Locating of breather hole is shown as Figure 3.4.

For breather hole of Figure 3.4, at least, do not allow its around  $\phi$  2.4 to block.

Figure 3.4 Location of breather

# (4) Ambient temperature

The temperature conditions for a disk drive mounted in a cabinet refer to the ambient temperature at a point 3 cm from the disk drive. The ambient temperature must satisfy the temperature conditions described in Section 1.4, and the airflow must be considered to prevent the DE surface temperature from exceeding  $60\,^{\circ}\text{C}$ .

Provide air circulation in the cabinet such that the PCA side, in particular, receives sufficient cooling. To check the cooling efficiency, measure the surface temperatures of the DE. Regardless of the ambient temperature, this surface temperature must meet the standards listed in Table 3.1. Figure 3.5 shows the temperature measurement point.

Figure 3.5 Surface temperature measurement points

Table 3.1 Surface temperature measurement points and standard values

| No. | Measurement point | Temperature |

|-----|-------------------|-------------|

| 1   | DE cover          | 60 °C max   |

3-6 C141-E195-02EN

## (5) Service area

Figure 3.6 shows how the drive must be accessed (service areas) during and after installation.

Figure 3.6 Service area

# **ACAUTION**

**Data corruption:** Avoid mounting the disk drive near strong magnetic sources such as loud speakers. Ensure that the disk drive is not affected by external magnetic fields.

**Damage:** Do not press the cover of the disk drive. Pressing it too hard, the cover and the spindle motor contact, which may cause damage to the disk drive.

**Static:** When handling the device, disconnect the body ground (500 k $\Omega$  or greater). Do not touch the printed circuit board, but hold it by the edges.

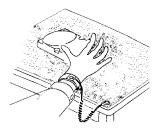

#### (6) Handling cautions

Please keep the following cautions, and handle the HDD under the safety environment.

#### - General notes

Wrist strap

Use the Wrist strap.

Shock absorbing mat

Place the shock absorbing mat on the operation table, and place ESD mat on it.

Do not hit HDD each other.

Do not stack when carrying.

Do not place HDD vertically to avoid falling down.

Do not drop.

Figure 3.7 Handling cautions

#### Installation

- (1) Please use the driver of a low impact when you use an electric driver. HDD is occasionally damaged by the impact of the driver.

- (2) Please observe the tightening torque of the screw strictly. M3 ······ 0.49N·m (5 kgf·cm).

## - Recommended equipments

| Contents |                  | Model                     | Maker       |  |

|----------|------------------|---------------------------|-------------|--|

| ESD      | Wrist strap      | JX-1200-3056-8            | SUMITOMO 3M |  |

|          | ESD mat          | SKY-8A (Color Seiden Mat) | Achilles    |  |

| Shock    | Low shock driver | SS-6500                   | HIOS        |  |

3-8 C141-E195-02EN

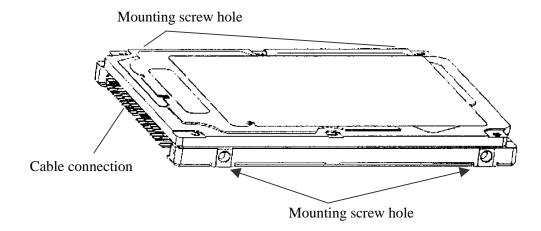

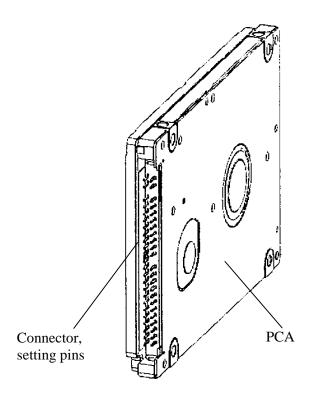

# 3.3 Cable Connections

# 3.3.1 Device connector

The disk drive has the connectors and terminals listed below for connecting external devices. Figure 3.8 shows the locations of these connectors and terminals.

**Figure 3.8 Connector locations**

# 3.3.2 Cable connector specifications

Table 3.2 lists the recommended specifications for the cable connectors.

Table 3.2 Cable connector specifications

|                                                    | Name                       | Model     | Manufacturer |

|----------------------------------------------------|----------------------------|-----------|--------------|

| ATA interface and power supply cable (44-pin type) | Cable socket (44-pin type) | 89361-144 | FCI          |

#### **IMPORTANT**

For the host interface cable, use a ribbon cable. A twisted cable or a cable with wires that have become separated from the ribbon may cause crosstalk between signal lines. This is because the interface is designed for ribbon cables and not for cables carrying differential signals.

#### 3.3.3 Device connection

Figure 3.9 shows how to connect the devices.

Figure 3.9 Cable connections

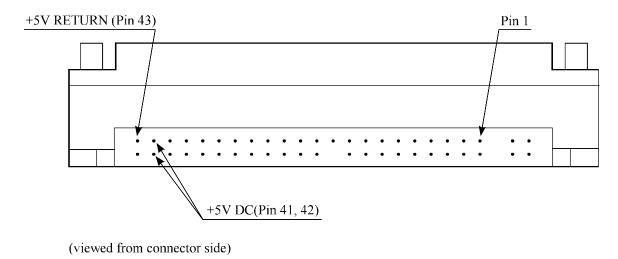

# 3.3.4 Power supply connector (CN1)

Figure 3.10 shows the pin assignment of the power supply connector (CN1).

3-10 C141-E195-02EN

Figure 3.10 Power supply connector pins (CN1)

# 3.4 Jumper Settings

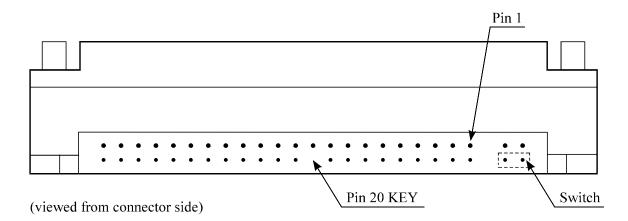

# 3.4.1 Location of setting jumpers

Figure 3.11 shows the location of the jumpers to select drive configuration and functions.

Figure 3.11 Jumper location

# 3.4.2 Factory default setting

Figure 3.12 shows the default setting position at the factory.

Figure 3.12 Factory default setting

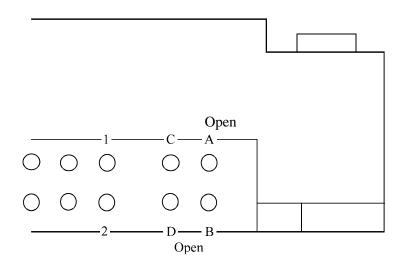

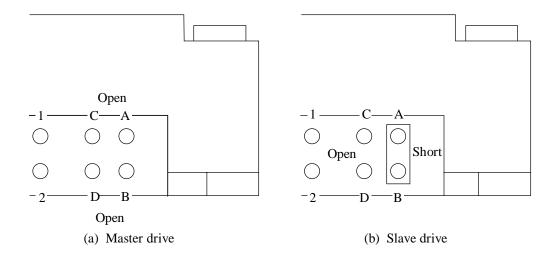

# 3.4.3 Master drive-slave drive setting

Master drive (disk drive #0) or slave drive (disk drive #1) is selected.

Figure 3.13 Jumper setting of master or slave drive

Note:

Pins A and C should be open.

3-12 C141-E195-02EN

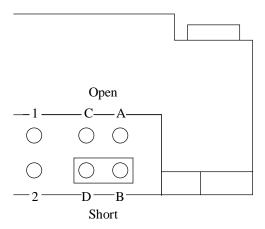

# 3.4.4 CSEL setting

Figure 3.14 shows the cable select (CSEL) setting.

Note:

The CSEL setting is not depended on setting between pins Band D.

# Figure 3.14 CSEL setting

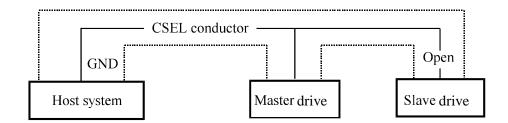

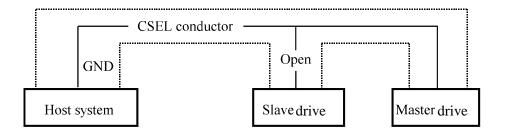

Figure 3.15 and 3.16 show examples of cable selection using unique interface cables.

By connecting the CSEL of the master drive to the CSEL Line (conducer) of the cable and connecting it to ground further, the CSEL is set to low level. The drive is identified as a master drive. At this time, the CSEL of the slave drive does not have a conductor. Thus, since the slave drive is not connected to the CSEL conductor, the CSEL is set to high level. The drive is identified as a slave drive.

Figure 3.15 Example (1) of Cable Select

Figure 3.16 Example (2) of Cable Select

# 3.4.5 Power Up in Standby setting

When pin C is grounded, the drive does not spin up at power on.

3-14 C141-E195-02EN

# **CHAPTER 4** Theory of Device Operation

4.1 Outline

4.2 Subassemblies

4.3 Circuit Configuration

4.4 Power-on Sequence

4.5 Self-calibration

4.6 Read/write Circuit

4.7 Servo Control

This chapter explains basic design concepts of the disk drive. Also, this chapter explains subassemblies of the disk drive, each sequence, servo control, and electrical circuit blocks.

#### 4.1 Outline

This chapter consists of two parts. First part (Section 4.2) explains mechanical assemblies of the disk drive. Second part (Sections 4.3 through 4.7) explains a servo information recorded in the disk drive and drive control method.

### 4.2 Subassemblies

The disk drive consists of a disk enclosure (DE) and printed circuit assembly (PCA).

The DE contains all movable parts in the disk drive, including the disk, spindle, actuator, read/write head, and air filter. For details, see Subsections 4.2.1 to 4.2.4.

The PCA contains the control circuits for the disk drive. The disk drive has one PCA. For details, see Sections 4.3.

#### 4.2.1 Disk

The DE contains disks with an outer diameter of 65 mm and an inner diameter of 20 mm.

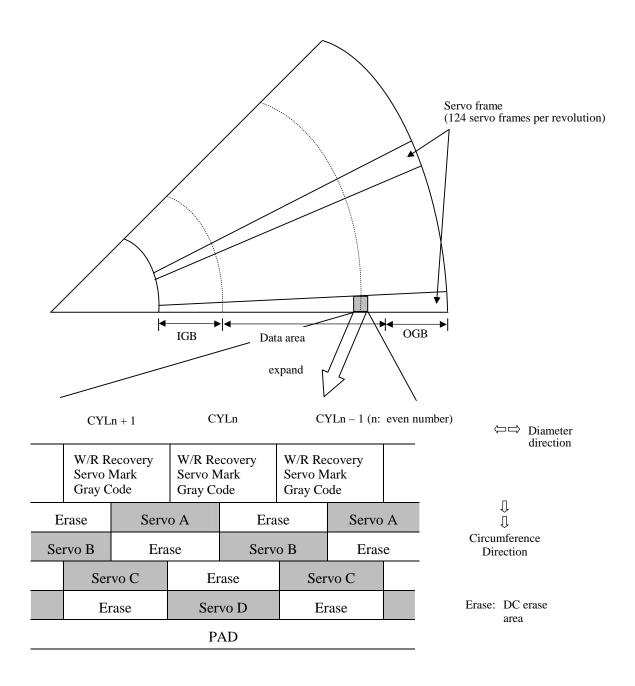

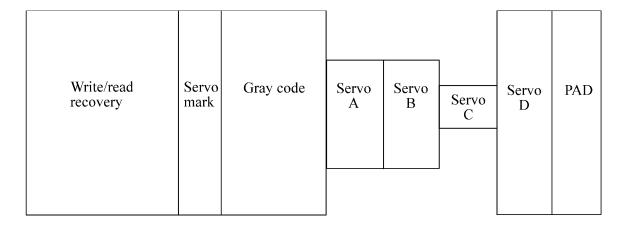

Servo data is recorded on each cylinder (total 124). Servo data written at factory is read out by the read head. For servo data, see Section 4.7.

# 4.2.2 Spindle

The spindle consists of a disk stack assembly and spindle motor. The disk stack assembly is activated by the direct drive sensor-less DC spindle motor, which has a speed of  $5,400 \text{ rpm} \pm 1\%$ . The spindle is controlled with detecting a PHASE signal generated by counter electromotive voltage of the spindle motor at starting.

#### 4.2.3 Actuator

The actuator consists of a voice coil motor (VCM) and a head carriage. The VCM moves the head carriage along the inner or outer edge of the disk. The head carriage position is controlled by feeding back the difference of the target position that is detected and reproduced from the servo information read by the read/write head.

4-2 C141-E195-02EN

#### 4.2.4 Air filter

There are two types of air filters: a breather filter and a circulation filter.

The breather filter makes an air in and out of the DE to prevent unnecessary pressure around the spindle when the disk starts or stops rotating. When disk drives are transported under conditions where the air pressure changes a lot, filtered air is circulated in the DE.

The circulation filter cleans out dust and dirt from inside the DE. The disk drive cycles air continuously through the circulation filter through an enclosed loop air cycle system operated by a blower on the rotating disk.

# 4.3 Circuit Configuration

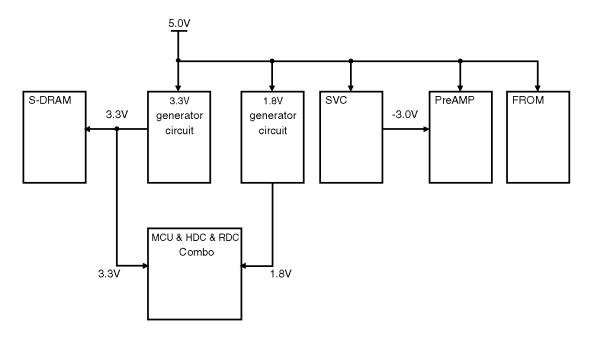

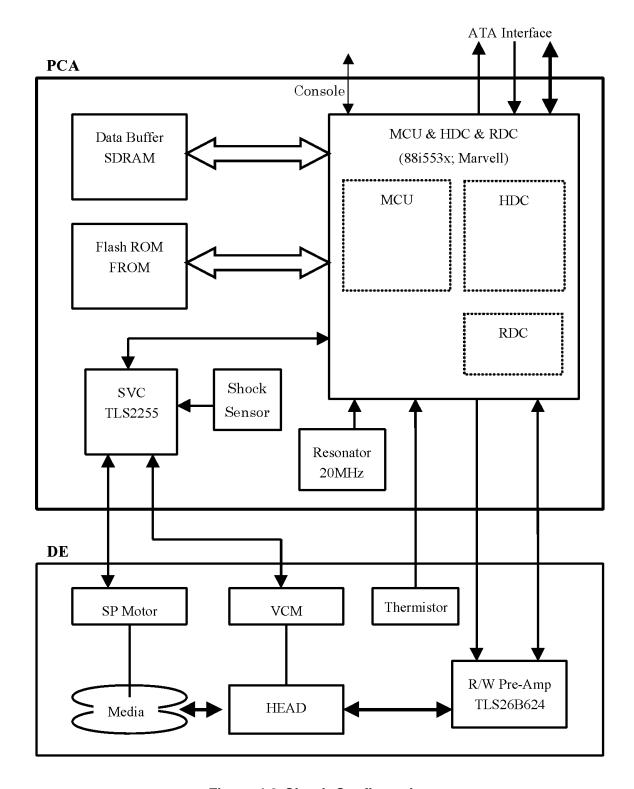

Figure 4.1 shows the power supply configuration of the disk drive, and Figure 4.2 shows the disk drive circuit configuration.

#### (1) Read/write circuit

The read/write circuit consists of two circuits; read/write preamplifier (PreAMP) and read channel (RDC).

The PreAMP consists of the write current switch circuit, that flows the write current to the head coil, and the voltage amplifier circuit, that amplitudes the read output from the head.

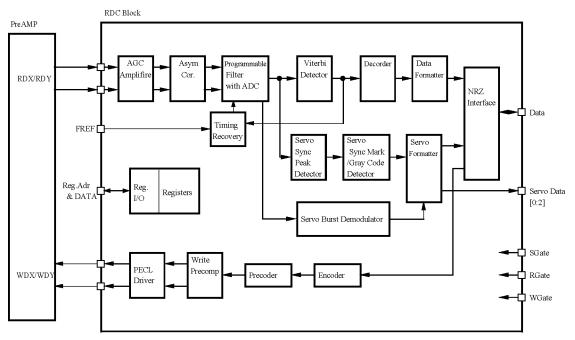

The RDC is the read demodulation circuit using the Modified Extended Partial Response (MEEPR) and Data-Dependent Media Noise Processor, and contains the Viterbi detector, programmable filter, adaptable transversal filter, times base generator, data separator circuits, 60/63 RLL (Limited) encoder Run Length and servo demodulation circuit.

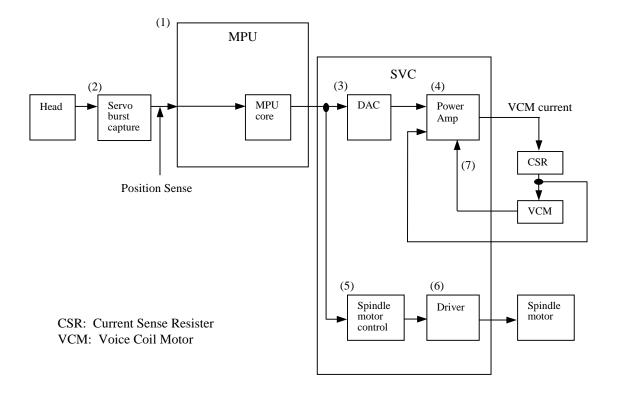

## (2) Servo circuit

The position and speed of the voice coil motor are controlled by 2 closed-loop servo using the servo information recorded on the data surface. The servo information is an analog signal converted to digital for processing by a MPU and then reconverted to an analog signal for control of the voice coil motor.

The MPU precisely sets each head on the track according on the servo information on the media surface.

#### (3) Spindle motor driver circuit

The circuit measures the interval of a PHASE signal generated by counterelectromotive voltage of a motor and controls the motor speed comparing target speed.

# (4) Controller circuit

Major functions are listed below.

- Data buffer management

- ATA interface control and data transfer control

- Sector format control

- Defect management

- ECC control

- Error recovery and self-diagnosis

Figure 4.1 Power Supply Configuration

4-4 C141-E195-02EN

**Figure 4.2 Circuit Configuration**

# 4.4 Power-on Sequence

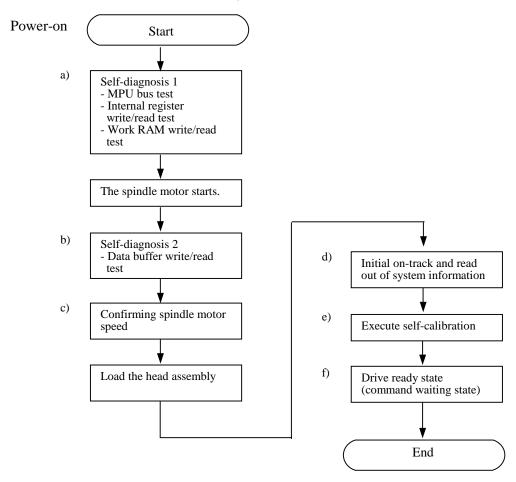

Figure 4.3 describes the operation sequence of the disk drive at power-on. The outline is described below.

- a) After the power is turned on, the disk drive executes the MPU bus test, internal register read/write test, and work RAM read/write test. When the self-diagnosis terminates successfully, the disk drive starts the spindle motor.

- b) The disk drive executes self-diagnosis (data buffer read/write test) after enabling response to the ATA bus.

- c) After confirming that the spindle motor has reached rated speed, the head assembly is loaded on the disk.

- d) The disk drive positions the heads onto the SA area and reads out the system information.

- e) The disk drive sets up a requirement for execution of self-seek-calibration. This collects data for VCM torque and mechanical external forces applied to the actuator, and updates the calibrating value.

- f) The drive becomes ready. The host can issue commands.

Figure 4.3 Power-on operation sequence

4-6 C141-E195-02EN

# 4.5 Self-calibration

The disk drive occasionally performs self-calibration in order to sense and calibrate mechanical external forces on the actuator, and VCM torque. This enables precise seek and read/write operations.

# 4.5.1 Self-calibration contents

#### (1) Sensing and compensating for external forces

The actuator suffers from torque due to the FPC forces and winds accompanying disk revolution. The torque vary with the disk drive and the cylinder where the head is positioned. To execute stable fast seek operations, external forces are occasionally sensed.

The firmware of the drive measures and stores the force (value of the actuator motor drive current) that balances the torque for stopping head stably. This includes the current offset in the power amplifier circuit and DAC system.

The forces are compensated by adding the measured value to the specified current value to the power amplifier. This makes the stable servo control.

To compensate torque varying by the cylinder, the disk is divided into 16 areas from the innermost to the outermost circumference and the compensating value is measured at the measuring cylinder on each area at factory calibration. The measured values are stored in the SA cylinder. In the self-calibration, the compensating value is updated using the value in the SA cylinder.

#### (2) Compensating open loop gain

Torque constant value of the VCM has a dispersion for each drive, and varies depending on the cylinder that the head is positioned. To realize the high speed seek operation, the value that compensates torque constant value change and loop gain change of the whole servo system due to temperature change is measured and stored.

For sensing, the firmware mixes the disturbance signal to the position signal at the state that the head is positioned to any cylinder. The firmware calculates the loop gain from the position signal and stores the compensation value against to the target gain as ratio.

For compensating, the direction current value to the power amplifier is multiplied by the compensation value. By this compensation, loop gain becomes constant value and the stable servo control is realized.

To compensate torque constant value change depending on cylinder, whole cylinders from most inner to most outer cylinder are divided into 14 partitions at calibration in the factory, and the compensation data is measured for representative cylinder of each partition. This measured value is stored in the SA area. The compensation value at self-calibration is calculated using the value in the SA area.

# 4.5.2 Execution timing of self-calibration

Self-calibration is performed once when power is turned on. After that, the disk drive does not perform self-calibration until it detects an error.

That is, self-calibration is performed each time one of the following events occur:

- When it passes from the power on for ten seconds and the disk drive shifts to Active Idle mode.

- The number of retries to write or seek data reaches the specified value.

- The error rate of data reading, writing, or seeking becomes lower than the specified value.

# 4.5.3 Command processing during self-calibration

This enables the host to execute the command without waiting for a long time, even when the disk drive is performing self-calibration. The command execution wait time is about maximum 72 ms.

When the error rate of data reading, writing, or seeking becomes lower than the specified value, self-calibration is performed to maintain disk drive stability.

If the disk drive receives a command execution request from the host while performing self-calibration, it stops the self-calibration and starts to execute the command. In other words, if a disk read or write service is necessary, the disk drive positions the head to the track requested by the host, reads or writes data, and then restarts calibration after 10 seconds.

If the error rate recovers to a value exceeding the specified value, self-calibration is not performed.

4-8 C141-E195-02EN

# 4.6 Read/write Circuit

The read/write circuit consists of the read/write preamplifier (PreAMP), the write circuit, the read circuit, and the time base generator in the read channel (RDC). Figure 4.4 is a block diagram of the read/write circuit.

# 4.6.1 Read/write preamplifier (PreAMP)

PreAMP equips a read preamplifier and a write current switch, that sets the bias current to the MR device and the current in writing. Each channel is connected to each data head, and PreAMP switches channel by serial I/O. In the event of any abnormalities, including a head short-circuit or head open circuit, the write unsafe signal is generated so that abnormal write does not occur.

#### 4.6.2 Write circuit

The write data is output from the hard disk controller (HDC) with the NRZ data format, and sent to the encoder circuit in the RDC. The NRZ write data is converted from 60-bit data to 63-bit data by the encoder circuit then sent to the HDIC, and the data is written onto the media.

#### (1) 32/34 RLL MEEPRML

This device converts data using the 60/63 RLL (Run Length Limited) algorithm.

# (2) Write precompensation

Write precompensation compensates, during a write process, for write non-linearity generated at reading.

Figure 4.4 Read/write circuit block diagram

# 4.6.3 Read circuit

The head read signal from the PreAMP is regulated by the automatic gain control (AGC) circuit. Then the output is converted into the sampled read data pulse by the programmable filter circuit and the flash digitizer circuit. This clock signal is converted into the NRZ data by the ENDEC circuit based on the read data maximum-likelihood-detected by the Viterbi detection circuit, then is sent to the HDC.

#### (1) AGC circuit

The AGC circuit automatically regulates the output amplitude to a constant value even when the input amplitude level fluctuates. The AGC amplifier output is maintained at a constant level even when the head output fluctuates due to the head characteristics or outer/inner head positions.

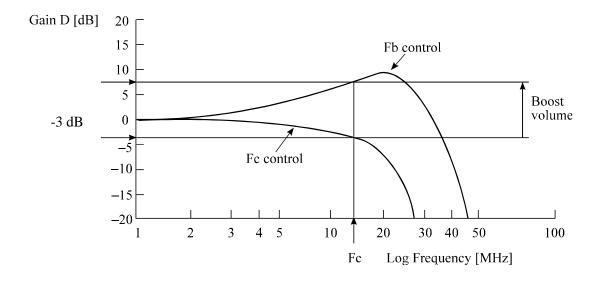

#### (2) Programmable filter circuit

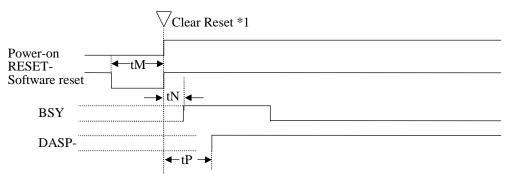

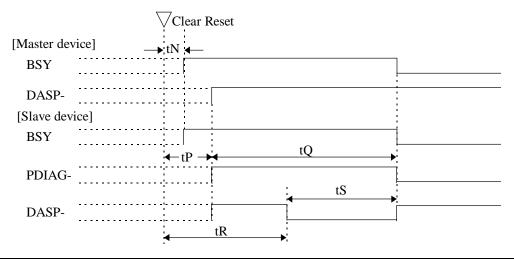

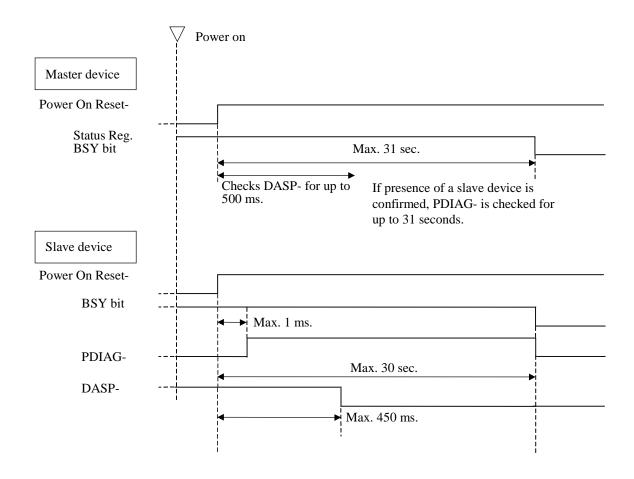

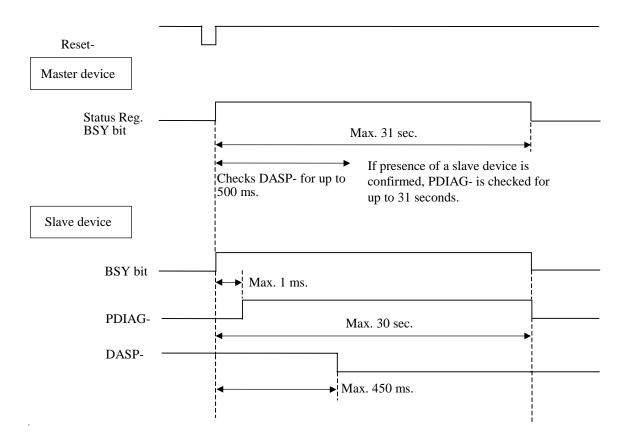

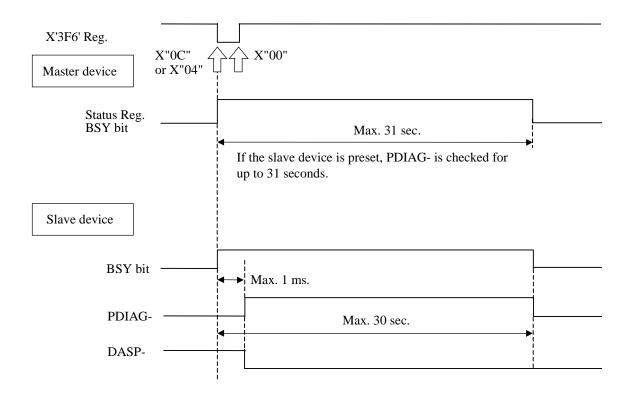

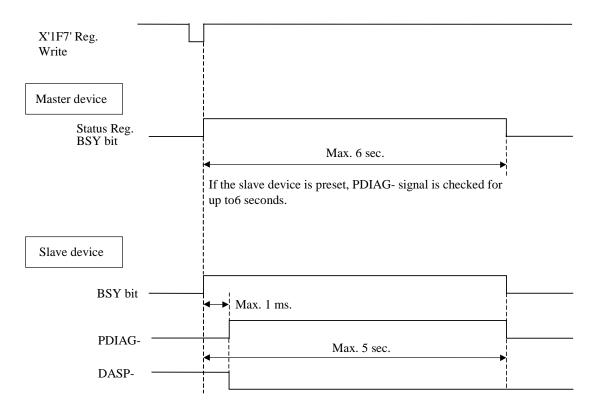

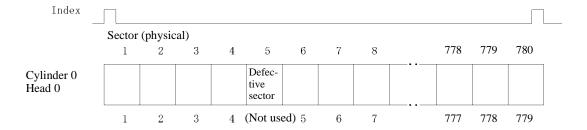

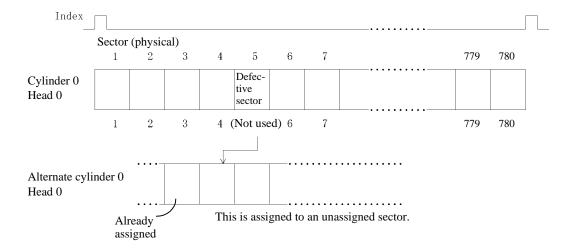

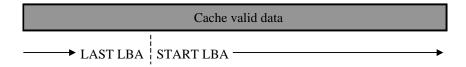

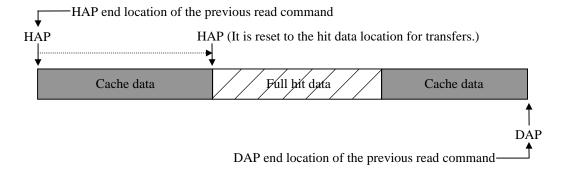

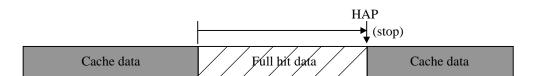

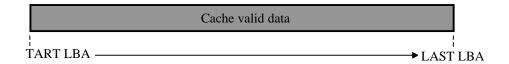

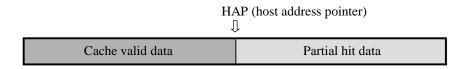

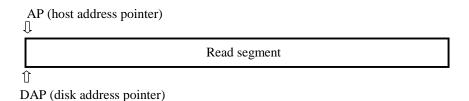

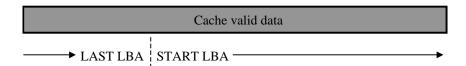

The programmable filter circuit has a low-pass filter function that eliminates unnecessary high frequency noise component and a high frequency boost-up function that equalizes the waveform of the read signal.